중국의 소형 드라이브 및 로봇 팔 종단 장치 전문 기업인 조델 로보틱스(Suzhou Jodell Robotics Co., Ltd.)가 '스마트공장·자동화산업전 2026(Automation World 2026, 이하 AW 2026)'에 참가해 생명 과학, 반도체, 신에너지 등 다양한 산업에 적용되는 초정밀 전동 그립퍼 솔루션을 선보였다. 스마트공장·자동화산업전 2026은 아시아 최대 규모 스마트공장 및 자동화산업 전문 전시회다. 이번 전시회는 3월 4일부터 6일까지 총 3일간 코엑스 전시장 전관에서 개최되며, '자율화, 지속가능성을 이끄는 힘(Autonomy, the Driver of Sustainability)'을 슬로건으로 내걸었다. 이번 전시에서 조델 로보틱스는 체외 진단 및 실험실 자동화 설비에 폭넓게 적용되고 있는 전동 회전 클립 'ERG32-150'과 전동 평행 클립 'EPG50-060'을 주력으로 소개했다. 이 제품들은 기존의 복잡한 그리퍼 장비 통합 설계를 크게 단순화한 일체형 구조로, 낙하 감지, 그랩 피드백, 전원 차단 자동 잠금 등 지능형 기능을 탑재하여 샘플 전처리 및 이액 분배 공정에서 작업자의 안전을 높이고 2차 오염을 방지한다. 또한

한화세미텍이 차세대 반도체 패키징의 핵심 장비로 꼽히는 2세대 하이브리드본더 개발을 완료하고 시장 공략에 나섰다. 기존 TC본더 성과에 이어 하이브리드 본딩 기술까지 확보하며 고대역폭 메모리(HBM) 장비 시장 선점에 속도를 낸다는 전략이다. 한화세미텍은 2세대 하이브리드본더 ‘SHB2 Nano’를 개발 완료했으며, 올해 상반기 중 고객사에 인도해 성능 테스트를 진행할 예정이라고 밝혔다. 2022년 1세대 하이브리드본더를 납품한 이후 4년 만에 이룬 성과로, 양산용 장비 상용화에 한 발 더 다가섰다는 평가다. 하이브리드본딩은 칩과 칩을 구리(Cu) 표면에 직접 접합하는 기술로, 16~20단 고적층 HBM을 얇은 두께로 구현할 수 있는 차세대 패키징 방식이다. 기존 범프 기반 접합과 달리 전도성 돌기가 없어 데이터 전송 속도를 높이고 전력 소모를 줄일 수 있다. 인공지능(AI) 반도체 확산과 함께 수요가 빠르게 증가하는 분야다. ‘SHB2 Nano’에는 위치 오차범위 0.1μm 단위의 초정밀 정렬 기술이 적용됐다. 이는 머리카락 굵기의 약 1/1000 수준으로, 고집적·초미세 패키징 공정에 요구되는 정밀도를 충족한다. 한화세미텍은 1세대 공급 경험을 기반으로

나노소재 전문기업 석경에이티가 2025년 연결 기준 매출 175억 원, 영업이익 39억 원을 기록하며 실적 개선에 성공했다. 매출은 전년 대비 27% 증가했고, 영업이익은 92.7% 급증했다. 영업이익률은 22.2%로 전년 대비 7.5%포인트 상승했다. 실적 성장은 주력 제품군의 고른 매출 확대가 견인했다. 3D 프린팅 소재 등 치과소재와 토너외첨제가 국내외 시장에서 안정적으로 성장하며 외형 확대를 이끌었다. 매출 증가에 따른 고정비 부담 완화와 함께 지급수수료 등 일부 일회성 비용 감소가 더해지며 수익 구조도 개선됐다. 기초 소재 사업 특성상 매출이 증가할수록 이익 레버리지 효과가 확대되는 구조가 확인됐다는 분석이다. 하반기에는 김제 제3공장 가동에 따른 감가상각비와 운영비 증가가 반영됐고, 5월 영암 제2공장 화재로 일시적 복구 비용이 발생했다. 다만 본사 공장을 통한 대체 생산 체계를 가동해 고객 공급은 안정적으로 유지했다. 현재는 복구가 완료돼 관련 비용은 대부분 해소된 상태다. 석경에이티는 반도체 패키징용 고기능성 실리카 소재 적용 확대에도 속도를 내고 있다. 저CTE 및 고기능 특성을 요구하는 차세대 패키징 공정에서 다수 고객사와 테스트를 진행 중

AI 반도체 확산 속 유리기판 공정 기술 경쟁 본격화 TGV 공정 핵심인 전기동도금, 장비기술력으로 승부 AI 반도체와 고성능 패키징 수요가 빠르게 확대되면서 유리기판 기반 공정 기술이 차세대 반도체 제조의 핵심 요소로 떠오르고 있다. 이런 흐름 속에서 글래스기판·복합동박 장비 전문기업 태성이 유리기판 TGV 공정을 겨냥한 핵심 장비 공급에 나서며 관련 산업 내 존재감을 키우고 있다. 태성은 금속 표면처리 전문 기업 E사에 TGV(Through Glass Via) Bottom-up Via Fill 방식의 전기 동도금 설비를 공급한다고 밝혔다. 이번에 공급되는 장비는 유리기판에 형성된 관통홀 내부를 아래에서 위로 균일하게 구리로 채우는 구조로, 유리기판 기반 반도체 패키징 공정에서 전기적 신뢰성과 공정 안정성을 확보하는 데 중요한 역할을 수행하는 설비다. TGV 공정은 유리기판을 활용한 차세대 패키징 기술에서 핵심으로 꼽힌다. 특히 관통홀 내부를 균일하게 채우는 도금 품질은 신호 안정성과 장기 신뢰성에 직접적인 영향을 미친다. 태성의 TGV Bottom-up Via Fill 전기 동도금 설비는 이러한 요구에 대응하기 위한 장비로, 향후 유리기판 공정 조건 검증

한미반도체는 반도체 전문가 이명호 부사장을 영입했다고 14일 밝혔다. 이명호 부사장은 반도체 분야에서 25년 이상 경력을 보유한 전문가로, 애플, 텍사스인스트루먼트, JCET·스태츠칩팩, 앰코테크놀로지 등 글로벌 반도체 기업에서 근무했다. 이들 기업에서 제품 개발과 공정 기술, 품질, 제조 전반을 아우르는 실무 경험을 쌓았으며, 이를 바탕으로 다양한 첨단 반도체 패키징 기술의 개발과 양산을 주도해 왔다. 애플에서는 2014년부터 약 10년간 근무하며 아이폰, 애플워치, 아이패드 등 주요 제품에 적용되는 애플리케이션 프로세서(AP)용 반도체 패키징 개발을 담당했다. 이와 함께 배터리 보호 회로(BMU) 개발도 총괄했다. 텍사스인스트루먼트에서는 2004년부터 약 10년간 재직하며 엔지니어링 매니저로서 다양한 글로벌 프로젝트를 이끌었다. 이명호 부사장은 한미반도체에서 개발과 영업을 총괄하며 신제품과 핵심 기술 개발 역량 강화에 주력할 예정이다. 또한 글로벌 고객사 확대와 전략적 협업을 통해 한미반도체의 사업 경쟁력을 한층 공고히 할 계획이다. 한미반도체 관계자는 “이명호 부사장의 합류는 글로벌 고객 대응 역량과 차세대 반도체 기술 경쟁력을 한 단계 끌어올리는 중요

반도체·디스플레이 장비 전문기업 에스티아이가 차세대 전력반도체용 방열 부품 제조 장비 개발에 성공하며 글로벌 전력반도체 시장에 본격 진출한다. 에스티아이는 중국 주요 전력반도체 제조사와 약 6,650만 달러 규모의 생산라인 구축 계약을 체결하며 고부가가치 전력반도체 장비 사업을 새로운 성장 축으로 확대할 계획이다. 이번 신제품은 전력반도체 모듈의 신뢰성과 효율을 결정짓는 방열 공정을 고도화한 장비로, 고전압·고주파 환경에서 운영되는 전력반도체 특성에 최적화된 기술이 적용되었다. 발열 관리가 전력반도체 성능·수명·안정성의 핵심 요인으로 부상하면서 글로벌 제조사들은 방열 부품의 성능 향상과 생산 효율 개선에 대한 투자를 확대한 바 있다. 방열 부품은 열방출을 통해 성능 저하를 막고 장비 수명을 늘리는 동시에 화재·폭발 위험을 줄이는 필수 구성 요소로 주목받고 있다. AI 고도화, HBM·인터포저 패키징 확산, 데이터센터 증설, 전기차(EV) 고성능화, 신재생에너지 인프라 확대 등으로 고효율 전력반도체 시장은 구조적 성장 국면에 진입했다. 이러한 환경에서 에스티아이는 독자 공법 기반의 방열 부품 제조 공정을 수년간 개발해 왔으며, 이번 프로젝트를 통해 기술력을 공

산업통상부 국가기술표준원은 26일 서울에서 삼성전자, SK하이닉스 등 국내 반도체 전문가 90여명이 참석한 가운데 ‘2025 반도체 표준화 포럼’을 개최했다고 밝혔다. 이번 포럼에는 세계 3대 반도체 표준화 기구인 IEC 반도체소자 기술위원회, 국제반도체장비재료협회(SEMI), 국제반도체표준협의회(JEDEC)의 전문가들이 참여해 첨단 반도체 패키징(후공정)과 인공지능(AI) 관련 반도체 표준화 동향을 논의했다. 먼저 IEC 분야에서는 우리나라가 지난주 일본에서 열린 IEC 반도체소자 회의에서 제안한 신규 국제표준안 2건이 소개됐다. 제안된 표준은 ▲범프 없이 웨이퍼 간 직접 접합하는 하이브리드 본딩 강도 평가방법 ▲전력반도체 웨이퍼 다이싱(절단) 정밀도 평가방법이다. 두 표준은 웨이퍼 접합과 칩(다이) 분리 공정의 신뢰성을 객관적으로 평가하기 위한 기준으로, 향후 국내 반도체 패키징 및 공정 장비 기업들이 글로벌 고객사와의 사양 정합 부담과 중복 시험 부담을 줄이는 데 기여할 것으로 기대된다. SEMI는 첨단 패키징 공장의 자동화 관련 표준화 이슈를 주제로 반도체 패널과 대형 기판의 이송·취급 등 자동화 운영 전반에 대한 표준화 활동을 소개했다. JEDEC은

AI 기반 제조지능화 솔루션 전문기업 피아이이(공동대표 최정일·김현준)가 산업통상자원부가 주관하는 ‘2025년도 소재부품기술개발사업’ 공동연구개발기관으로 선정됐다. 이번 과제는 필옵틱스가 주관하며 총 85억6천만 원 규모로 4년간 추진된다. 목표는 차세대 반도체 패키징용 유리기판 기술의 글로벌 경쟁력 확보다. 해당 과제의 정식 명칭은 ‘반도체 패키징 유리기판용 레이저 스캐닝 TGV 공정기술 및 공정장비 개발’로, 피아이이는 TGV(Through Glass Via) 고정밀 검사 측정 장비 개발을 담당한다. TGV는 반도체 패키징 공정에서 유리기판을 관통하는 미세 홀(Via)을 형성하는 핵심 기술로, 고집적·고성능 패키징에 필수적인 차세대 공정이다. 피아이이는 홀로토모그래피(Holotomography) 기술과 AI 검사 플랫폼을 결합한 정밀 검사 솔루션을 개발해 유리기판의 미세 결함을 3D로 정밀 측정할 계획이다. 빛의 위상과 강도를 기록해 내부 굴절률 분포를 3차원으로 재구성함으로써 TGV 홀 내부, 기판 모서리의 미세 크랙, 표면 거칠기(Roughness) 등을 고정밀로 분석할 수 있다. 해당 기술은 비접촉·비파괴 방식으로 적용돼 검사 대상물에 손상을 주지

인하대학교는 최근 수원 컨벤션센터에서 ‘2025 테스트기술 워크숍(Test Technology Workshop 2025)’을 성황리에 개최했다고 31일 밝혔다. 이번 워크숍은 인하대 반도체특성화대학사업단과 한국반도체테스트학회가 공동 주관했으며, 국내 주요 반도체 기업과 연구기관의 전문가들이 참석해 반도체 테스트 및 패키징 분야의 최신 기술 동향과 산업 전망을 공유했다. 올해 워크숍에서는 ▲첨단 패키징 환경에서의 테스트 기술 고도화 ▲AI 반도체 및 칩렛(Chiplet) 구조 확산에 따른 신뢰성 확보 ▲차세대 반도체 공정과 테스트 자동화 기술 등 산업계 주요 이슈가 집중적으로 다뤄졌다. 박준용 경희대 교수, 임종수 아주대 교수, 김현돈 삼성전자 PL, 정우식 SK하이닉스 부사장 등이 발표자로 참여해 최신 연구 동향과 산업 트렌드를 공유했으며, 이어진 세션에서는 기술적 과제와 향후 발전 방향에 대한 심도 있는 토론이 진행됐다. 특히 이번 워크숍에서는 한국반도체테스트학회 표준위원회가 주도한 메모리 테스트(JETEC) 표준화 문서 ‘SPS-KTC001(2025)’이 처음으로 공개됐다. 해당 표준화 작업은 2021년부터 삼성전자, SK하이닉스, Teradyne, Ad

ST마이크로일렉트로닉스는 프랑스 투르(Tours) 사업장에 차세대 패널 레벨 패키징(PLP: Panel-Level Packaging) 기술 개발을 위한 새로운 파일럿 라인을 구축한다고 30일 밝혔다. 해당 라인은 2026년 3분기 가동을 목표로 하고 있으며, 총 6000만 달러 이상의 자본 투자가 투입될 예정이다. PLP는 반도체 칩 제조 공정의 효율성과 경제성을 동시에 높이는 첨단 패키징 기술이다. 기존의 원형 웨이퍼 대신 대형 직사각형 패널을 사용함으로써 생산 효율을 극대화하고, 제조 단가를 낮추는 것이 특징이다. 이 기술은 전자기기의 소형화, 고성능화, 비용 효율성을 향상시키는 핵심 공정으로, 대량 생산에 최적화된 자동화 패키징 및 테스트 솔루션으로 평가받고 있다. ST는 현재 말레이시아에서 운영 중인 1세대 PLP 라인과 글로벌 연구개발(R&D) 네트워크를 기반으로 차세대 PLP 기술 개발을 추진 중이다. 이번 투르 파일럿 라인은 ST의 기존 기술력과 인프라를 확장해 자동차, 산업용, 컨슈머 전자 등 다양한 제품군에 PLP 적용을 확대하는 전략적 거점으로 활용될 예정이다. 파비오 구알란드리스 ST 품질·제조·기술 부문 사장은 “투르 사업장의 P

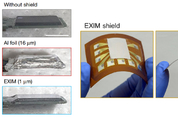

광주과학기술원(GIST) 신소재공학과 연한울 교수 연구팀이 서울대학교 주영창 교수, 고려대학교 김명기 교수, 한국과학기술연구원(KIST) 이성수 박사 연구진과 함께 세계 최고 수준의 초박막 전자파 차폐막을 개발했다. 이번 연구는 금속과 2차원 세라믹 소재 ‘맥신(MXene)’을 결합한 새로운 이종접합 구조를 설계해, 기존 차폐막보다 100배 이상 향상된 전자파 차단 성능을 구현한 것이 핵심이다. 이 기술은 전자파 차폐막을 얇게 만들면 성능이 급격히 떨어지는 이른바 ‘두께-성능 딜레마’를 근본적으로 해결했다는 점에서 학계와 산업계의 주목을 받고 있다. 연구 결과는 과학 저널 ‘네이처(Nature)’에 10월 30일 온라인 게재됐다. 맥신은 금속과 탄소(또는 질소) 원자층이 교대로 쌓인 2차원 구조의 세라믹 소재로, 우수한 전도성과 유연성을 동시에 지닌 차세대 전자소재다. GIST 연구팀은 별도의 미세기공(pore) 구조를 만들지 않고, 기존 반도체 패키징 공정 장비만으로 금속과 맥신을 교차 적층한 ‘EXIM(Embedded-MXene-in-Metal)’ 구조를 구현했다. 이 구조에서 금속층은 전자파를 반사하고, 맥신층은 이를 산란·흡수함으로써 얇은 두께에서도

램리서치가 인공지능(AI)과 고성능 컴퓨팅(HPC) 시대의 요구에 맞춰 새로운 첨단 패키징 장비 ‘VECTOR TEOS 3D’를 선보였다. 이번 장비는 3D 다이 적층과 고밀도 이종 집적 과정에서 발생하는 웨이퍼 휨, 공극, 크랙 등 다양한 기술적 난제를 해결하기 위해 개발됐다. VECTOR TEOS 3D는 램리서치가 오랜 기간 축적한 유전체 증착 기술과 웨이퍼 처리 노하우가 집약된 장비다. 특히 업계 최대 두께 수준의 공극 없는 다이 간 충진 필름을 구현할 수 있으며, 심하게 휘어진 웨이퍼에도 균일한 증착이 가능하다. 세샤 바라다라잔 램리서치 글로벌 제품 그룹 수석 부사장은 “이번 장비는 AI 시대로 나아가는 반도체 제조업체들의 요구를 충족하는 차별화된 솔루션”이라고 강조했다. AI 반도체는 대규모 데이터를 빠르게 처리하기 위해 여러 개의 다이를 칩렛 구조로 집적하는 방향으로 발전하고 있다. 하지만 다이가 두꺼워지고 복잡해질수록 공정 스트레스로 인한 웨이퍼 변형이나 필름 불량이 발생하기 쉽다. VECTOR TEOS 3D는 나노 단위 정밀도를 바탕으로 최대 60마이크론 두께의 특수 유전체 필름을 안정적으로 증착하며, 필요 시 100마이크론 이상까지도 확장할

마이크로칩테크놀로지의 자회사 실리콘 스토리지 테크놀로지(Silicon Storage Technology, SST)와 반도체 패키징 전문기업 데카 테크놀로지(Deca Technologies)는 고객이 모듈형 멀티 다이 시스템을 쉽게 도입할 수 있도록 지원하는 비휘발성 메모리(NVM) 칩렛 패키지 공동 개발을 위한 전략적 협력을 체결했다고 11일 밝혔다. 이번 협력은 SST의 SuperFlash 임베디드 플래시 기술과 데카의 M-Series 팬아웃 및 Adaptive Patterning 기술을 결합, 고객이 NVM 칩렛 기반 시스템을 설계·검증·상용화할 수 있는 통합형 플랫폼 제공을 목표로 한다. 이를 통해 단일 다이 설계 대비 유연성과 기술·상업적 이점을 제공할 예정이다. 공동 개발 솔루션은 SuperFlash 기술과 인터페이스 로직, 칩렛 독립 동작을 위한 물리적 설계 요소를 포함하며 데카의 RDL 설계 규칙, 시뮬레이션 플로우, 테스트 전략 및 검증된 파트너 에코시스템을 통한 제조 경로를 함께 적용한다. 이를 통해 설계 단계부터 검증, 프로토타입 생산까지 지원하며 설계 주기 단축과 이종집적 기술 확산을 가속화한다. 로빈 데이비스 데카 전략 협력·애플리케이션

한국과학기술원(KAIST) 반도체공학대학원은 8일 오후 대전 본원 전기·전자공학부동(E3-2)에서 이광형 KAIST 총장, 이장우 대전시장 등이 참석한 가운데 반도체 연구를 지원하는 첨단장비센터 개소식을 열었다. 이번에 도입되는 첨단장비는 반도체 소자·소재와 패키징 분야 연구에 활용될 핵심 인프라로, 설계부터 시뮬레이션·제작·평가까지 반도체 개발 전 과정을 아우르는 통합 연구 환경을 제공한다. KAIST 교수·학생뿐만 아니라 지역 기업과 연구기관에도 개방돼 산학연 협력 거점 역할을 할 것으로 기대된다. KAIST는 글로벌 반도체 설계 소프트웨어 기업 시높시스코리아에서 반도체 공정·소자 시뮬레이션 소프트웨어(TCAD) 라이선스를 기부받아 반도체 교육·연구 인프라를 갖추게 됐다. 이와 함께 2028년까지 국비 150억 원, 시비 49억 원 등 215억 원을 투입해 전기및전자공학부·신소재공학과·물리학과·기계공학과·생명화학공학과 교수진 34명이 참여하고, 반도체 분야에서 225명 이상의 석·박사급 고급 인재를 양성할 계획이다. 현재 반도체공학대학원에는 123명이 재학 중이며, 산학 컨소시엄 20여 개 기업과 협력 프로젝트를 수행하는 등 가시적 성과를 내고 있다. 이

PCB와 반도체 패키징 산업의 현재와 미래 국내 최대 PCB 및 반도체 패키징 전문 전시회인 제22회 ‘국제첨단반도체기판 및 패키징산업전(KPCA Show 2025)’이 지난 9월 3일부터 5일까지 인천 송도컨벤시아에서 열렸다. 올해 슬로건은 ‘Beyond AI & Angstrom, 한계를 넘다’로, 역대 최대 규모인 250여 개 기업, 750개 부스가 참가해 차세대 기판과 첨단 패키징 기술을 선보였다. 이번 KPCAShow는 단순 전시를 넘어 시장 전망과 기술 동향을 공유하는 자리로 의미를 더했다. 글로벌 어드밴스트 패키징 시장은 2024년 396억 달러에서 2030년 550억 달러로 성장할 것으로 예상되며, AI 가속기와 칩렛 구조 확산으로 2.5D·3D 패키징, HBM 수요가 급격히 늘고 있다. 동시에 하이브리드 본딩, 팬아웃 패널 레벨 패키징(PLP), 글래스 코어 서브스트레이트 등 차세대 기술이 주목받고 있다. 이러한 흐름 속에서 전시회에 참가한 주요 기업들의 기술 경쟁력은 전시회의 또 다른 핵심이다. 국내외 250여 개 기업이 기판, 소재, 장비, 검사 솔루션 등 다양한 영역에서 최신 기술을 전시해 업계 관계자들의 관심을 끌었다. KPCA