아바고 테크놀로지스의 ACPL-339J는 고급 1.0A 듀얼 출력 지능형 IGBT 게이트 드라이브 옵토커플러이다. 시스템 설계자는 다양한 정격 전류의 MOSFET 버퍼를 지원하도록 설계된 ACPL-339J를 통해 MOSFET

버퍼와 파워 IGBT/MOSFET 스위치를 교환함으로써 하나의 하드웨어 플랫폼으로 각각 다른 시스템 정격

출력을 지원할 수 있다.

아바고 테크놀로지스의 ACPL-339J가 가진 콘셉트는 모터 제어 및 저출력에서 고출력까지 모두 커버하는 출력 변환 애플리케이션용 게이트 드라이브 설계의 확장성을 극대화시킨다. 단락 방지 기능, 저전압 방지(UVLO ; Under Vol-tage Lockout) 기능, ‘소프트’ IGBT 턴오프 및 고장 절연 피드백 기능이 일체화된 ACPL-339J는 최대의 설계 유연성과 회로 보호를 제공한다.

여기서는 ACPL-339J 지능형 게이트 드라이버의 UVLO 및 불포화 감지(DESAT ; Desaturation Sensing) 탐지 기능을 정확히 예측 및 시뮬레이션할 수 있는 Avago SPICE 매크로 모델의 기능에 대해 알아 본다.

UVLO 기능은 ACPL-339J의 출력에서 전력 공급이 부족할 때 IGBT와 같이 비싼 파워 반도체 소자가 켜지지 않도록 하는 반면, DESAT 회로는 단락 이벤트 발생을 탐지한 후 즉시 IGBT의 ‘소프트’ 셧다운을 진행한다. 이 두 기능은 교대로 작동함으로써 고가의 IGBT가 높은 열 방출로 인해 파손되지 않도록 한다.

UVLO 기능

IGBT 게이트 전압이 부족하면 IGBT의 턴온 저항이 증가하면서 출력 손실이 커지는데, 이로 인한 열 방출 때문에 IGBT가 파손될 수 있다. ACPL-339J는 출력 전원 공급을 지속적으로 모니터한다. 출력 전원 공급이 UVLO 임계치보다 낮으면 게이트 드라이버 출력이 차단되면서 IGBT를 저전압 바이어스로부터 보호한다. ACPL-339J에는 UVLO_P와 UVLO_N 등 두 개의 UVLO 로직 블록이 있으며, 각각 VOUTP와 VOUTN을 제어한다.

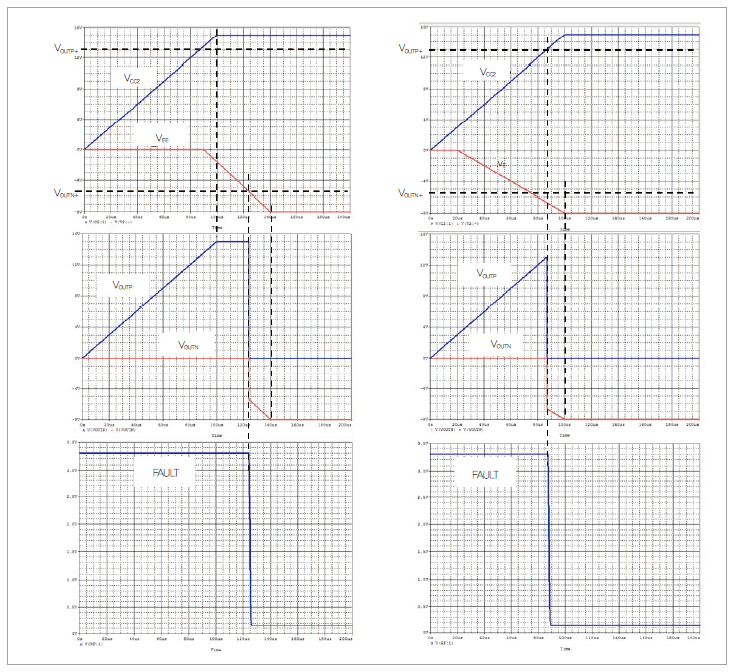

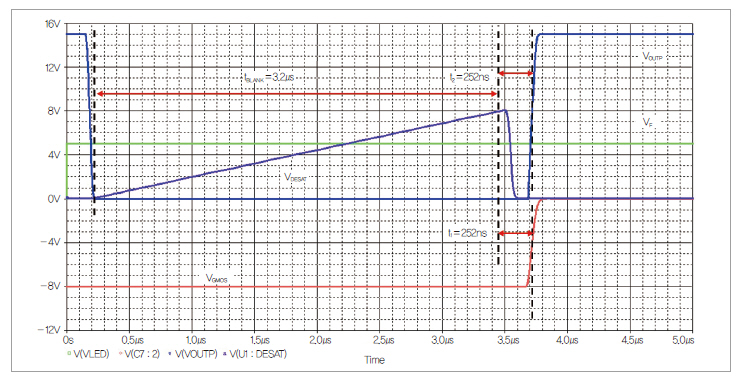

UVLO 제어 논리는 입력 IF와 DESAT보다 우선한다. 다시 말해 VCC2 및 VEE 공급이 UVLO 클램프를 활성화시키는 데 충분하지 않으면 IF와 DESAT가 무시된다. VUVLOP+와 VUVLON+는 클램프가 해제되기 전에 서로 교차되므로, VOUTP와 VOUTN은 IF와 DESAT에 따라 동작한다. 이러한 내용이 그림 1의 SPICE 시뮬레이션 플롯에 나타나 있다.

그림 1. SPICE에서 시뮬레이션한 UVLO, VOUT 및 FAULT 논리 다이어그램

DESAT 탐지 및 ‘소프트’ 셧다운

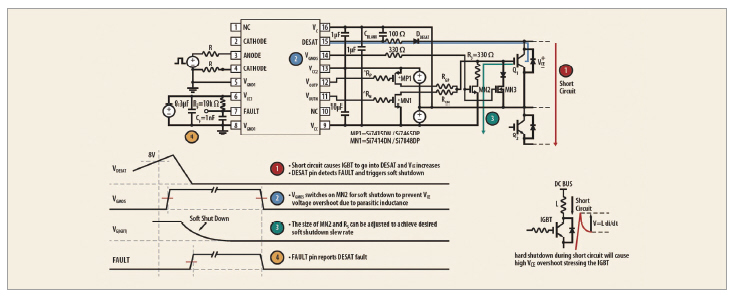

IGBT의 컬렉터-이미터 전압은 IGBT가 정상적으로 작동하는 동안 ACPL-339J DESAT 핀으로 모니터된다. 단락이 발생하면 높은 전류가 IGBT를 통과하여 포화 상태에서 DESAT 모드로 접어든다. 이에 따라 IGBT의 컬렉터와 이미터 전압이 포화 전압 2V부터 급증한다. ACPL-339J의 임계치 8V를 넘어서면 단락 고장이 등록되고 소프트 셧다운이 작동한다.

ACPL-339J의 VGMOS 핀은 외부 트랜지스터를 작동시키고 IGBT의 게이트를 서서히 방출하여 소프트 셧다운 효과가 있도록 한다. 소프트 셧다운 속도는 외부 트랜지스터와 저항기 사이즈로 조절할 수 있다. 마지막으로, DESAT 동작은 내장된 절연 피드백 경로를 통해 컨트롤러에 고장을 보고함으로써 완료된다. 그림 2는 단락 이벤트 시 DESAT 탐지 동작을 단계별로 나타낸 것이다.

그림 2. 단락 방지 및 ‘소프트’ IGBT 턴오프 및 고장 절연 피드백

그림 3. 단락 탐지를 보여주는 SPICE 시뮬레이션 회로

그림 4. LED, DESAT, VOUTP 및 VGMOS 플롯

표 1. 데이터 통상 규격과 시뮬레이션 결과 비교

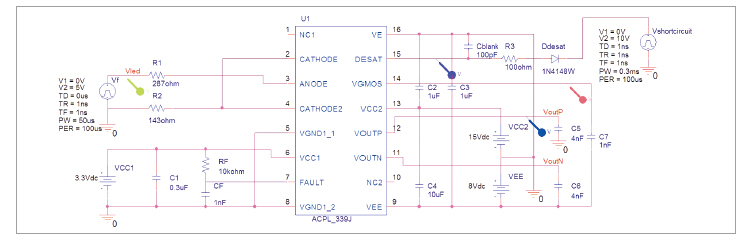

DESAT 핀은 IGBT VCE 전압을 모니터한다. DESAT 고장 탐지 회로는 컬렉터 전압이 DESAT 임계치 이하로 떨어지도록 하기 위해, IGBT가 켜진 후 짧은 시간이라도 반드시 꺼져 있어야 한다. DESAT 블랭킹 타임이라고 하는 이 시간은 DESAT 충전 전류(ICHG), DESAT 전압 (VDESAT) 및 외부 DESAT 커패시터(CBLANK)에 의해 조절된다. 명목 블랭킹 타임은 다음 식과 같이 계산할 수 있다.

TBLANK=CBLANK×VDESAT/ICHG

데이터 시트에 있는 규격에 따르면, VDESAT의 일반 값은 8V이고 ICHG는 일반적으로 250㎂이다. 100pF의 축전기가 사용될 경우, 블랭킹 타임은 100pF×8V/250㎂=3.2μsec이다. 정전 용량의 값을 약간 증가시켜 블랭킹 타임을 조절할 수도 있지만, 100pF보다 작은 값은 권장하지 않는다. 이 명목 블랭킹 타임은 또한 ACPL-339J가 DESAT 고장 상태에 반응하는 데 걸리는 최장 시간을 나타낸다. 그림 3의 시뮬레이션 회로는 DESAT 탐지 동작에 대해 나타낸 것이다.

DESAT 다이오드의 기능은 IGBT가 켜진 상태에서 순방향 전류를 전도시켜 IGBT의 포화된 컬렉터-이미터 전압 VCESAT를 감지하도록 하는 한편, IGBT가 꺼졌을 때 고전압을 차단한다. IGBT가 꺼져 있는 동안 DESAT 다이오드의 순방향 전도가 끝나 가면서 짧은 시간 역전류가 흐른다. 이 역회복 효과로 인해 다이오드는 접합부의 이동전하가 소멸될 때까지 차단 기능을 달성하지 못한다.

이 시간 동안에는 공통적으로 IGBT의 컬렉터-이미터에 걸친 dVCE/dt가 매우 높아진다. 이는 블랭킹-커패시터 CBLANK를 충전시키는 ICHARGE-CD-DESAT×dVCE/dt 충전 전류로 이어진다. 이 충전 전류를 최소화하고 DESAT의 오작동을 피하기 위해 회복이 빠른 다이오드의 사용을 권장한다.

IGBT에 걸쳐 연결된 프리휠링(Freewheeling) 플라이백 다이오드의 경우 다이오드의 순시 순방향 전압을 크게 초과하는, 순시 순방향 과도 전압이 있을 수 있다. 이로 인해 DESAT 핀에서 큰 마이너스 전압 스파이크가 일어나며, 보호 기능이 사용되지 않을 경우 상당한 전류가 드라이버 밖으로 도출될 수 있다.

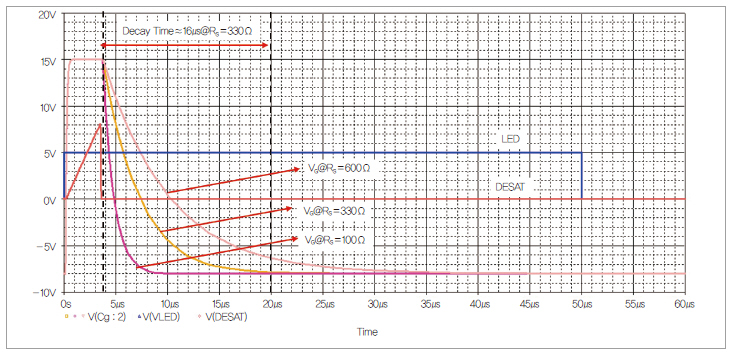

이 전류가 드라이버 IC를 파손하지 않도록 제한하려면 DESAT 다이오드와 직렬로 100Ω 저항기를 삽입해야 한다. 저항이 추가된다고 해도 DESAT 임계치나 DESAT 블랭킹 타임이 바뀌지는 않는다. SPICE 시뮬레이션에서 정확히 예측된 블랭킹 타임은 그림 4와 같으며, 표 1에는 데이터시트 통상 규격에 맞게 조율된 VGMOS 및 VOUTP 지연 시간이 나타나 있다.

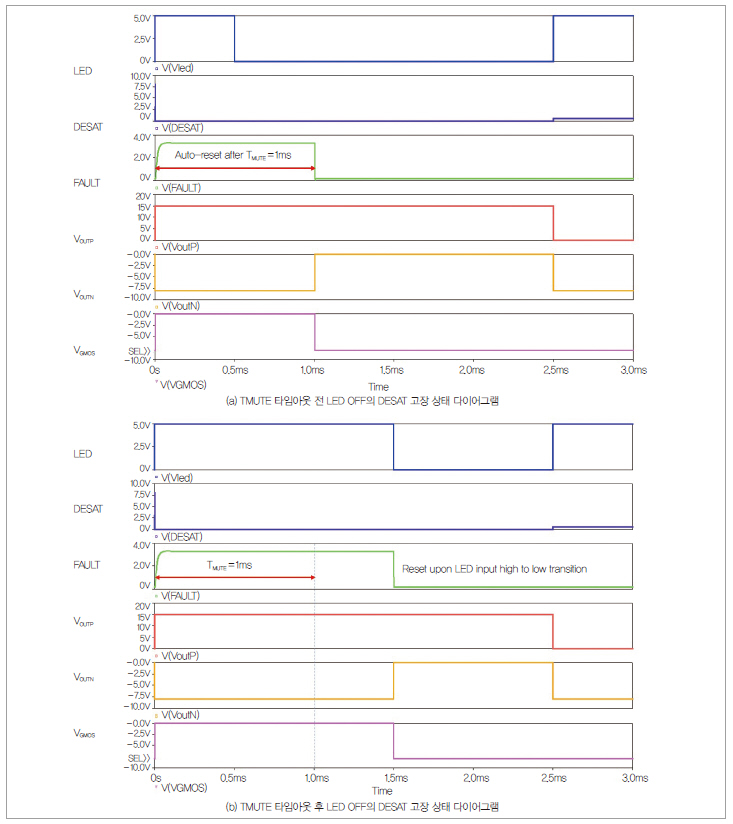

DESAT 고장이 탐지되고 TBLANK 시간이 지나면 VOUTP와 VOUTN이 각각의 MP1과 MN1을 끈다. TMUTE 시간 동안 출력은 발생하지 않는다. 이 시간 동안 모든 입력 LED 신호는 드라이버가 IGBT를 완전히 소프트 셧다운 하도록 무시된다. 나중에 1ms의(통상적인) 침묵 시간(TMUTE)이 경과하거나 LED 출력이 높은 곳에서 낮은 곳으로 전환된다고 해도 고장은 자동 리셋된다. 이와 같이 최소 타임아웃이 존재하며 연장도 가능하다. 그림 5(a)와 그림 5(b)는 시뮬레이션 상황을 나타낸 것이다.

그림 5. TMUTE 타임아웃 전후 LED OFF의 DESAT 고장 상태 다이어그램

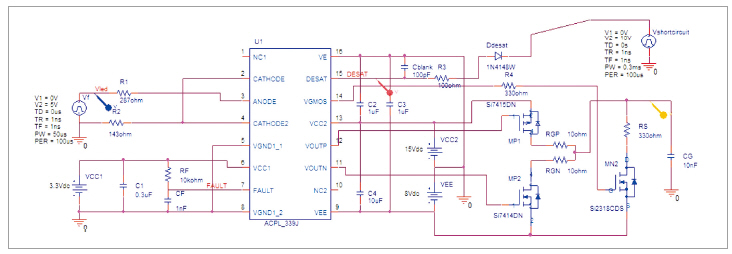

마지막으로 단락이 발생하는 실제 예를 살펴보기 위해 그림 6과 같이 SPICE 시뮬레이션 회로를 구성해 보자. 전반적인 시뮬레이션의 정확도를 높이기 위해 외부 MOS 소자의 SPICE 모델도 포함했다. IGBT SPICE 모델은 이 시뮬레이션에서 사용되지 않으며 IGBT의 게이트 정전 용량을 모의하기 위해 10nF 축전기로 대체되었다.

그림 6. 권장 외부 MOS 구성 요소의 SPICE 모델을 포함한 SPICE 시뮬레이션 적용 회로

그림 7. 각각 다른 저항기의 RS 값을 선택하여 IGBT 소프트 셧다운 감쇠 시간 변경

DESAT 고장이 탐지되면 VGMOS는 LOW에서 HIGH로 전환되면서 외부 MN2 풀 다운 소자를 켜게 된다. MN2는 RS의 RC 상수와 IGBT의 입력 정전 용량 CIN에 해당하는 감쇠율로 IGBT 게이트를 서서히 방전시킨다. RS 330Ω과 CIN 10nF을 기준으로 한 전체 소프트 셧다운은 4.8×330Ω×10nF=15.8㎲ 속도로 감쇠된다. 소프트 셧다운은 리드와 와이어 인덕턴스로 인해 전압 스파이크를 일으킬 수 있는 컬렉터 전류의 급격한 전하 이동을 방지한다. 또한 각각 다른 저항기 RS 값을 선택하여 IGBT 소프트 셧다운 감쇠 시간을 변경할 수도 있다(그림 7).

여기서는 ACPL-339J SPICE 매크로 모델이 전력 공급 부족과 단락 현상 시 고가 IGBT를 파손으로부터 방지하는 두 가지 메커니즘, UVLO와 DESAT의 특성에 대해 알아 보았다. 설계 엔지니어는 각각 다른 조건에서 적용 회로를 시뮬레이션하여 복잡한 출력 논리를 쉽게 이해하고, 전체 회로의 성능을 예측할 수 있다. 또한 통상적인 데이터 시트 규격에 맞춰 정확히 조율된 DC와 AC 변환 매개변수를 이용함으로써 외부 요소를 보다 적절하게 선택할 수도 있다. 따라서 ACPL-339J SPICE 매크로 모델을 복잡한 회로 시뮬레이션과 적용 요건에 맞게 활용할 수 있다.

그리고 아바고 테크놀로지스에서 제공하는 각종 옵토커플러 장치 매크로 모델은 http://www.avagotech.com/pages/optocouplers_plastic/spicemodels/에서 다운로드할 수 있다.

참고문헌

1. Tee Chun Keong, “Driving and Protecting IGBTs In Inverter Applications” Power Electronics, Aug 30, 2013

2. Jamshed Namdar Khan, “SPICE Circuit Simulations for the HCNR200 and HCNR201 Analog Optocouplers”, AV02-3334EN Application Note

3. “ACPL-339J Dual Output Gate Drive Optocoupler Interface with Integrated(VCE) DESAT Detection, FAULT and UVLO Status Feedback”, AV02-3784EN Datasheet, June 10, 2013

Lim Shiun Pin / Avago Technologies