미드엔드 파운드리 개발

지난 40년 동안 반도체 디자인, 제조, 패키징 기술 발전이 현대 전자산업의 혁신을 결정해 왔다. 회로 밀도와 프로세싱 능력이 18개월마다 두 배로 늘어난다는 무어의 법칙은 업계의 일화에 머무르지 않고 전자 산업의 발전을 유도하는 핵심 원동력으로까지 발전하게 됐다. 반도체 산업은 이제 정교하고 복잡한 전체 공급망을 통해 해마다 수십억 개의 IC 생산을 지원하는동시에 계속해서 더 복잡해지며 규모를 키우고 있다.

Tomas Bauer SILEX MICROSYSTEMS

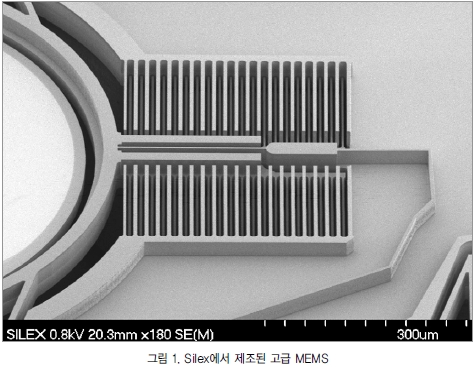

실렉스마이크로시스템즈(Silex Microsystems)는 고급 MEMS (Microelectromechanical Systems) 소자 제 조 시장의 필요성을 충족시키기 위해 2000년에 설립됐다. MEMS 소자는 아 이디어를 확실한 대량 생산 체계로 바 꾸는 데 있어서 제조상 독특한 어려움 을 갖고 있다. 고객의 엄격한 품질 및 신 뢰성 요건을 충족시키며 기존 IC들과 집적시키는 MEMS 소자 패키징 작업은 매우 까다롭다. 이러한 점은 MEMS 소 자, CMOS 웨이퍼의 MEMS 프로세싱, CMOS-MEMS 웨이퍼 레벨 패키징을 내놓은 실렉스마이크로시스템즈에게 지난 10년 동안 패키징 및 제조 기술 혁 신의 엔진이 됐다.

IC 및 MEMS 세계는 지난수년동안 별도의 독립적인 생산으로 운영되다가 패키지 레벨, 모듈 레벨에서만 결합되 는 식으로 공존해왔다. 그러나 무어의 법칙을 쫓아가는 것이 점점 더 어려워 지고, 작아지는 풋프린트에 더 큰 프로 세싱 기능을 담아야 하는 압력 때문에 업계는 새로운 솔루션을 찾으려 하고 있다. 이에 따라 가장 촉망되는 후보로 3D 패키징이 등장하고 있다. 다양한 기 술을 다루는 3D IC는 여러 개의 칩을 하나의 패키지 안에 통합시키는 적층형 다이 솔루션으로 적층형 와이어본드와 플립 칩, 실리콘 인터포저를 사용하거 나 이 솔루션들을 조합하여 사용하고 있다. 업계에서 3D 패키징에 대해 말할 때 모바일 SoC와 메모리를 주로 이야기 하지만, 실제로는 센서에 전력을 제공 하는 RF의 수많은 기능들이 이미 이와 동일한 솔루션들을 구현하며 유닛 면적 당 기능 문제를 해결하고 있다.

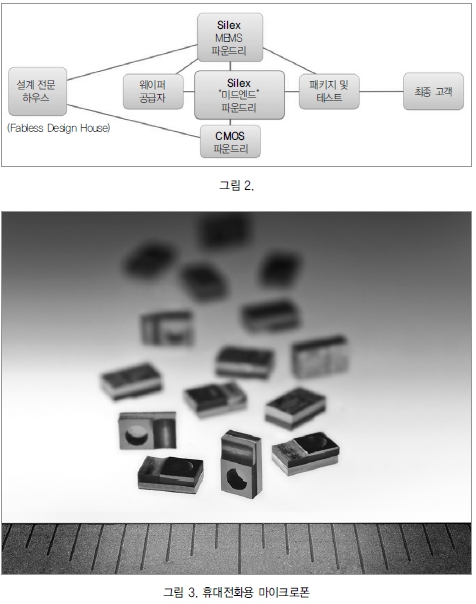

그러나 이러한 기술을 실행하려면 웨 이퍼 단계에서 프로세싱할 수 있는 새 로운 기능, 특히 TSV 제조와 인터포저 를 위한 RDL 금속화 또는 적층형 ASIC 이 필요하다. 이와 같은 업계의 추세에 따라, MEMS 고객들에게 이미 동일한 솔루션을 제공해온 실렉스마이크로시 스템즈 파운드리의 다양한 기술과 경험 을 활용해야 한다는 요구 또한 증가하 고 있다. 이에 따라 완전히 프론트엔드 도 백엔드도 아닌, 새로운“미드엔드 파 운드리”라는 카테고리가 업계에 등장했 는데, 이것은 이미 실렉스마이크로시스 템즈에서 서비스하고 있는 분야이다.

Sil-Via : 5년 이상 확립된 TSV 플랫폼

Sil-Via를 통한 올-실리콘 풀 웨이퍼 두께의 산업 표준인 실렉스마이크로시 스템즈 Sil-Via 솔루션은 2003년에 휴 대폰용 고급 MEMS 마이크로폰을 지원 하기 위해 개발되기 시작했다. 2006년 에 시장에 출시된 후, Sil-Via 기술은 100개 이상의 제품과 50,000개 이상의 웨이퍼에서 사용되고 있다.

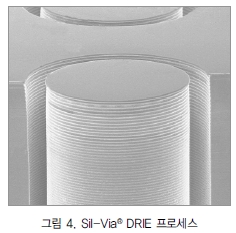

Sil-Via는 저항이 낮은 기판과 고급 MEMS DRIE 프로세싱을 이용하여 실 리콘 기판을 통해 올-실리콘 필라(pillar) 나 비아(via)를 만들어낸다. 이 비아 에 산화물이 채워지면 테라옴 (TeraOhm) 수준의 무결성으로 완전히 절연된 비아가 만들어진다. 임베디드 동공이 밀폐 웨이퍼와 결합되면 MEMS 구조를 위한 완벽한 패키징 솔루션이 실현되어 기능성과 신뢰성이 극대화되 고, 컴포넌트 풋프린트는 최소화된다. 실렉스마이크로시스템즈는 마이크로 폰, 가속도계, 유량 센서, 자이로, IC 인 터포저, 랩온칩 (Lab-on-Chips), 마이 크로미러, 옵티컬 벤치, 압력 센서, 프린 트 헤드, 공명기, 마이크로 배터리 등 십 여 개 이상의 프로젝트에서 Sil-Via TSV를 구현해 왔다. 이로 인해 Sil-Via 의 비아는 MEMS 애플리케이션을 위한 양산형 TSV의 산업 벤치마크가 됐다.

Sil-Via 기술로 가능해진 실리콘 인터포저 솔루션

MEMS를 IC에 집적할 때, 또는 서로 다른 IC들을 하나의 패키지에 수직으로 집적할 때에는 종종 지형학적인 문제가 발생한다. 본드 패드의 경우 TSV가 액 티브 영역이나 물리적인 크기의 제약 때 문에 제대로 정렬되지 않는 경우가 많은 데, 이로 인해 실제 패드 연결 상단 부위 에서 파워와 시그널의 버싱(bussing)이 필요할 수 있다. 실리콘 인터포저는 구 조적인 장점과 RDL (Redistribution Layer) 탄력성, 양면 범프, 루트 능력 등 으로 이러한 문제를 해결하고 있다.

실렉스마이크로시스템즈의 Sil-Via기술은 2.5D와 3D용의 매우 탄력적인 실리콘 인터포저 솔루션을 가능하게 한 다. 300mm∼600mm의 웨이퍼를 위 해 50㎛까지 낮춘 Sil-Via 피치는 I/O 인텐시브 ASIC에 대한 고밀도를 지원 한다. 기판 물질로 만들어진 Sil-Via의 싱글 크리스털 구조는 다른 물질을 사 용하는 다른 비아들의 큰 고민 중 하나 인 팽창 온도 계수에 있어서 주변 기판 에 완벽하게 일치되는 비아를 만들어냈 다. 비아를 기판에 단리시키면 1테라옴 을 초과하여, 확실하게 낮은 저항의 제 로 누출 TSV 비아에 도움이 된다.

기타 3D 통합 솔루션들

기본 회로와의 연결을 유지하고 밀폐 무결성을 확보하면서 실리콘에 붙이는 것은CMOS-to-MEMS 패키징에서 매 우 중요한 일이다. 에칭 동공을 가진 실 리콘 웨이퍼는 그 아래의 MEMS 구조를 방해하거나 훼손하는 일 없이 웨이퍼 레 벨의 패키징을 제공하기 위해 고안된 것 이다. TSV를통해연결성을제공해야하 며, 완성된 CMOS 웨이퍼를 이 패키징 프로세스에서 사용하려면 웨이퍼 본딩 은100% CMOS 호환이가능해야한다.

실렉스마이크로시스템즈는 이러한 문제를 해결하기 위해 통합 플랫폼을 기 초로 하여 Met-CapR 메탈 비아를 개발 했다. 부분적으로 채워진 풀 웨이퍼 두 께의 메탈 비아는 CMOS와 완전히 호환 되는 AuSi 공융 웨이퍼 본드와 결합하 여 완벽한 웨이퍼 레벨의 솔루션이 된 다. 웨이퍼의 앞면부터 뒷면까지 전체 비아 저항은 20밀리오옴 미만이다.

MEMS는 CMOS에서 어떤“무어의 법칙”을 적용할 수 있는가?

MEMS 고유의 기능을 통합이 필요한 고급 IC들과 조합시킬 경우, 새로운 패 키징 기능을 이용할 수 있는 길이 열리 게 된다.

“Functional Capping”이란 이러한 진화를 설명할 때 쓰는 말이다. 바이패 스, RF, 시그널 조절 패시브를 웨이퍼 캡에 통합시킬 수 있게 되면 한 차원 더 높은 기능과 통합이 동일한 풋프린트 내에서 달성되는 것이다.

메탈 및 실리콘 비아와의 결합 능력, 임베디드 MEMS 장치를 위한 동공, 밀 봉 웨이퍼 씰, 제로-크로스토크 준비로 가능해진 액티브 영역 아일랜드 등이 의미하는 것은 미래의 통합 패키지 솔 루션이 진정한 의미의 시스템 온 칩을 가능하게 한다는 것이다.

Copyright ⓒ 첨단 & Hellot.net