통합 또는 외부 MOSFET을 가진 동기식 스텝다운 파워 컨버터는 개발자가 효율에 영향을 미치는 파라미터들과 데이터시트의 자세한 사항을 이해할 경우 그 효율을 높일 수 있다. 이상적인 전력 컨버터가 없는 상황에서 개발자는 절충과 균형으로 전원 공급 장치의 효율에 영향을 미치는 파라미터들을 최적화해야 한다. 여기서는 전원 공급 장치의 몇 가지 기본 원리에 대해 논의해 보고, 스위칭 전압 레귤레이터의 전력 단계인 MOSFET이 효율에 미치는 영향에 대해 살펴본다.

전원 공급 장치의 효율은 오늘날 클라우드 인프라 하드웨어에서 중요한 기준 중 하나이다.

선택한 전원 솔루션의 효율은 집적회로(IC), 인쇄회로기판(PCB), 기타 데이터 센터 전력 사용량의 유효성을 결정하는 부품들의 시스템 전력 손실 및 열 성능과 관련이 깊다.

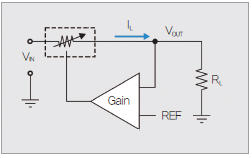

그림 1에 나타난 선형 레귤레이터의 경우, 전력 손실과 효율은 식 (1)과 식 (2)로 정해진다.

▲ 그림 1. 전형적인 선형 레귤레이터

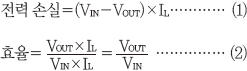

그리고 그림 2에 나타난 이상적인 스위칭 레귤레이터의 경우, 스위치가 열리면 전류와 전력 손실이 제로로 된다. 따라서 VIN이 절단된다. 스위치가 닫히면 스위치를 지나는 전압이 제로가 되고 전력 손실도 제로가 된다. 이상적인 스위치란 제로 손실을 의미하며, 따라서 100% 효율을 제공한다. 하지만 부품들은 다음 예시에서 알 수 있듯이 이상적으로 존재하지는 않는다.

▲ 그림 2. 스위치가 열려 있는 이상적인 스위칭

레귤레이터

효율적인 스위칭 레귤레이터는 열 방산이 적어 히트싱크, 팬 및 어셈블리와 같은 구성요소들의 시스템 비용과 크기를 절감해 준다.

배터리 구동 시스템에서 전력 손실이 적다는 것은 디바이스가 그 배터리에서 뽑아내는 전류가 적기 때문에 같은 배터리로도 더 오랜 시간 동안 작동할 수 있다는 뜻이다.

효율에 기여하는 여러 요소들을 살펴보기 위해 여기서는 논점을 스텝다운(벅) DC/DC 컨버터 토폴로지에 맞췄다. 이 토폴로지는 오늘날 클라우드 인프라 시스템에서 가장 대중적인 스위칭 레귤레이터이다.

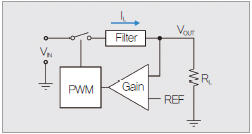

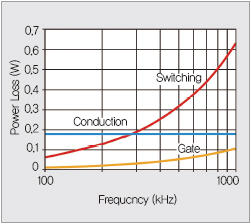

그림 3은 벅 컨버터의 주요 전력 손실 원인인 전도 손실, 스위칭 손실, 정전(정지) 손실을 나타낸 것이다.

▲ 그림 3. 벅 스위칭 레귤레이터의 전력 손실 요인들

MOSFET은 한정적인 스위칭 시간을 갖고 있다. 따라서 스위칭 손실은 턴온/턴오프에 걸리는 시간 동안 MOSFET이 반드시 처리해야 하는 동적 전압 및 전류에서 나오게 된다.

인덕터의 스위칭 손실은 코어 및 코어 손실에서 비롯된다. 게이트-드라이브 손실 또한 스위칭 손실이다. FET를 온/오프 하는 데 있어서 이것이 필요하기 때문이다.

제어 회로의 경우, 정지 전류가 전력 손실에 기여한다. 비교기가 빠를수록 바이어스 전류가 높다.

피드백 회로의 경우에는 전압 디바이더, 오차증폭기, 비교기 바이어스 전류가 전력 손실에 영향을 미친다. 메가옴(Megaohm) 레지스터는 전력 손실을 줄이는 데 사용할 수 없다. 그 이유는 피드백 회로로 들어오는 바이어스 전류 때문이다.

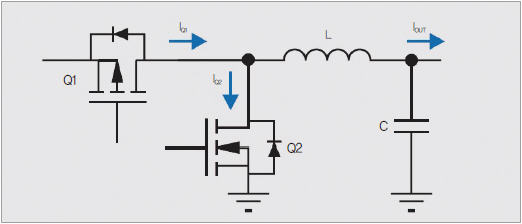

그림 4는 기본적인 스위칭 회로이며, 식 (3)을 이용해 Q1 또는 Q2의 전도 손실을 계산했다.

▲ 그림 4. MOSFET 전도 손실

R은 선택한 MOSFET의 RDS(on)이고, I는 그 MOSFET을 거치는 실효(Root-Mean-Square ; RMS) 전류이며, 또한 둘 중 어느 쪽도 스위칭 주파수와 함수 관계에 있지 않다는 점에 유의해야 한다.

일반적으로 스위칭 주파수가 높고 입력 전압이 높을수록 낮은 QG(게이트 전력)로 그 스위치 MOSFET(Q1)의 스위칭 손실을 줄여야 한다.

정류기 MOSFET(Q2)의 경우, 낮은 RDS(on)이 가장 중요하지만, 게이트 전력을 간과해서는 안 된다.

또한 MOSFET RDS(on)를 변경하면, 듀티사이클(D)도 바뀌어 다른 곳의 RMS 전류와 손실에 영향을 미치게 된다. 인덕터 전류 역시 MOSFET 전도 손실에 영향을 미친다.

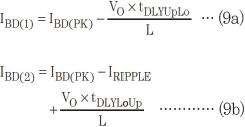

그림 5의 경우 하이사이드 MOSFET (Q1) 스위칭 손실이 좀더 복잡하므로 이를 제일 먼저 평가했다. 손실 방정식을 유도하기 위한 그림 5의 관계는 다음과 같다.

▲ 그림 5. MOSFET 스위칭 손실

• Et1=(VDS×ID/2)×t1

• Et2=(VDS/2×ID)×t2

• PSW=2×(Et1+Et2)×fSW

• t1=QGS2/IG

• t2=QGD/IG

• VPLAT=밀러 플래토(Miller Plateau)

• VTH=게이트 투 소스 스레숄드 전압

• IG=Cdv/dt

• Q=C×V

• dt=t1 또는 t2

• VGS(Actual)는 MOSFET을 구동하는 실제 게이트 투 소스 드라이브 전압

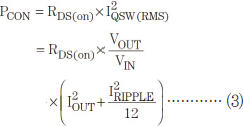

MOSFET 스위칭 손실은 식 (4)와 같이 부하 전류 및 전원 공급 장치의 스위칭 주파수와 함수관계에 있다.

여기서 VIN=VDS(드레인 투 소스 전압), IOUT=ID(드레인 전류), fSW는 스위칭 주파수, IG는 게이트 전류이며 QGS2와 QGD는 드라이버가 FET를 충전하는 데 걸리는 시간에 좌우된다.

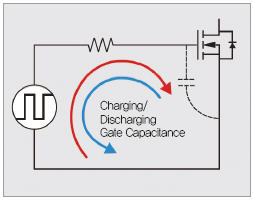

스위치-MOSFET 게이트 손실이 발생하는 것은 MOSFET 게이트를 충전하는 데 필요한 에너지 때문일 수 있다. 이것이 게이트 전압 위치의 QG(TOT)이다. 이는 턴온 및 턴오프 게이트 손실 둘 다에 해당한다.

이 전력의 대부분은 MOSFET 게이트 드라이버에 있다. 게이트-드라이브 손실은 주파수에 따라서 좌우되며, MOSFET의 게이트 정전용량과 함수관계에 있다.

MOSFET을 켜고 끌 때, 스위칭 주파수가 높을수록 게이트-드라이브 손실도 높아진다. 이는 스위칭 주파수가 올라가면 효율이 떨어지는 또 다른 이유이기도 하다.

MOSFET이 크고 RDS(on)가 낮을수록 전도 손실은 낮아지지만 게이트 정전용량은 높아지며, 이 경우 게이트-드라이브 손실도 높아진다.

이러한 손실은 멀티플 메가헤르츠(Multiple-megahertz) 영역의 매우 높은 스위칭 주파수에서(외부 MOSFET을 가진) 전원 공급 장치 컨트롤러에 큰 손실을 가할 수 있다. 특정 상황에서 ‘최상의’ QG 및 RDS(on)를 계산하는 방법으로 실증된 것은 없다. 물론 FOM(Figure Of Merit) 수치들이 일반적으로 데이터시트에서 (FOM=RDS(on)×QG)로 언급되기는 한다.

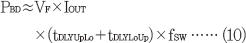

그림 6에 나타난 스위치 MOSFET의 경우, 식 (5)의 낮은 게이트 전력(QG)이 전력 손실을 낮춰 주고 스위칭 시간을 빨라지게 할 수 있다.

▲ 그림 6. 스위치 MOSFET 게이트 손실

그러나 이것은 정류기 MOSFET에 더 많은 과류 턴온을 일으킨다. 이러한 거래를 수용할 수 있는 설계에서 적절한 부분을 찾을 수 있다.

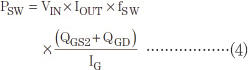

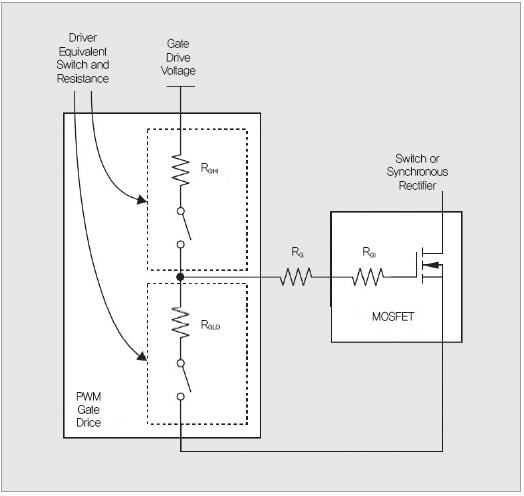

그림 7과 같이 일반적인 게이트 손실도 있다. 게이트-드라이브 IC에 미치는 MOSFET 효과 또는 게이트 드라이버가 집적된 PWM(Pulse Width Modul-ation) 컨트롤러가 전력 방산 손실을 가중시킨다.

▲ 그림 7. 일반 게이트 손실

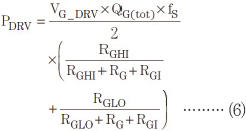

식 (6)에서 알 수 있듯이, 게이트-드라이브 손실이 모두 다 MOSFET에서 일어나는 것은 아니다.

• PDRV는 드라이버 손실을 계산하기 위해서 총 게이트 드라이브 손실을 나눈 것

• RGHI는 드라이버 턴온

• RGLO는 드라이버 턴오프

• RGHI를 RG로 바꾼 것이 게이트 레지스터 손실

• RGHI를 RGI로 바꾼 것이 스위칭 FET 손실

• QG가 높을수록 드라이버 방산 증가

• 외부 RG를 추가하면 내부 드라이버 방산이 감소하는데, 그 이유는 MOSFET 게이트의 전체 저항 경로를 줄여주기 때문이다.

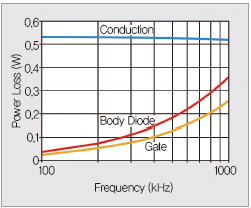

그림 8은 전체 스위치 MOSFET 손실의 다양한 요인들을 나타낸 것이다. 이제 정류기(동기식) MOSFET의 총 손실과 전도 손실을 따져 보자.

▲ 그림 8. 총 스위치 MOSFET 손실

정류기 MOSFET 전력 손실의 경우 전도 손실(PCON), 바디-다이오드 전도 손실(PBD), 게이트 손실(PGATE)로 이루어져 있다.

스위칭 손실이 없는 이유는 바디 다이오드 때문이다. 바디 다이오드가 전도하고 FET를 가로지르는 전압은 다이오드 전압으로 제로이다. 바디 다이오드는 식 (7)에 따라 제로-전압 스위칭을 보장해 준다.

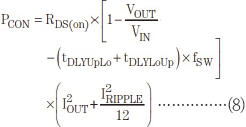

MOSFET 채널이 식 (8)에 따라 전도할 때 전도 손실은 단순한 I2R 손실이다.

• R은 선택된 MOSFET의 RDS(on)

• I는 MOSFET을 거치는 RMS 전류

• tDLYUpLo는 상위 MOSFET 턴오프와 하위 MOSFET 턴온 사이의 딜레이

• tDLYLoUp는 하위 MOSFET 턴오프와 상위 MOSFET 턴온 사이의 딜레이

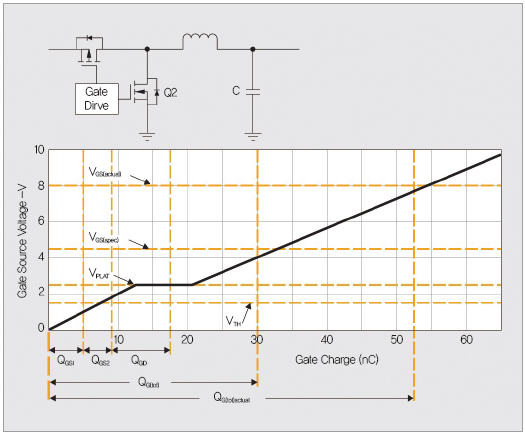

정류기 MOSFET 또한 바디-다이오드 손실을 갖고 있다. 평균적인 바디-다이오드 전류의 경우 데드타임 중에 계산할 수 있다.

그림 9의 청색 파형은 데드타임을 나타낸다. 이것은 하이사이드 FET가 턴오프할 때와 로우사이드 FET(정류기 FET)가 턴온할 때의 중간 시간을 의미한다. 그 스위칭 사이클에서 평균 전류를 구한다.

▲ 그림 9. 정류기 MOSFET 바디-다이오드 전류

출력 인덕터(L)의 경우에는 점선 IBD1, IBD2, IBD3의 기울기를 좌우한다. 이 기울기는 바디 다이오드를 거치는 평균 전류이다.

다음과 같이 식 (10)을 이용하면 바디-다이오드 전력 손실의 근사치를 계산할 수 있다.

그림 10에서 마지막으로 고려할 점은 정류기 MOSFET(Q2)의 게이트 손실에 대한 것이다. 게이트 손실은 스위치 MOSFET과 동일한 방식으로 계산한다. 높은 게이트 전력 때문에 손실이 클 수 있다.

▲ 그림 10. 정류기 MOSFET 게이트 드라이버 및 손실

그림 11은 정류기 MOSFET으로 인한 총 손실에 영향을 미치는 여러 원인들을 나타낸 것이다.

▲ 그림 11. 총 정류기 MOSFET 손실

☆

텍사스 인스트루먼트(TI)에서 전력 블록(한 패키지의 듀얼-MOSFET)과 전력단(한 패키지의 게이트 드라이버와 듀얼 MOSFET)을 비롯해 개별 MOSFET에 대한 포트폴리오를 다양하게 제공하고 있다.

MOSFET을 사용하는 전원 공급 장치 컨트롤 IC는 벅 PWM 컨트롤러와 SWIFTTM 통합 MOSFET 벅 컨버터(아날로그 및 PMBusTM)이다.

PWM 컨트롤러의 예시가 TPS40428 듀얼-출력/듀얼 위상, PMBus, 드라이버가 없는 PWM 컨트롤러이다. 이것은 CSD95378B NexFETTM 스마트 전력단과 쌍을 이루고 있다. SWIFT 통합- FET 컨버터의 예시는 TPS544C25이다. 이것은 주파수 동기화 30A PMBus 벅 컨버터이다. 이 디바이스에는 통합 MOSFET이 포함되어 있으며 이 글의 모든 설계 방정식을 적용할 수 있다.

George Lakkas _ 텍사스인스트루먼트

Copyright ⓒ 첨단 & Hellot.net