전력 전자 시스템을 위한 차세대 고전력 디바이스로서 최근 GaN FET의 활용도가 높아지고 있다.[1] GaN FET는 2차원 전자 가스(2DEG) 채널의 높은 캐리어 이동성에 의한 저전력 손실과, 대형 임계 전계로 인한 높은 파괴 전압으로 초고전력 밀도 동작을 실현한다.

또한 GaN FET는 주요 캐리어 디바이스이므로 역회복 전하가 없어 고전압 동작 가치가 높다. 여기서는 GaN이 차세대 DC-DC 컨버터에서 에너지 효율, 전력 밀도, 솔루션 크기를 어떻게 개선하는지 알아본다.

GaN FET가 가진 특성은 모두 높은 전환 주파수 동작에서 전력 손실을 줄여주는 전력 전자 애플리케이션에 적합하다고 할 수 있다.

합리적인 가격으로 실리콘 기판에서 GaN(Gallium-Nitride) 디바이스를 제작할 수 있게 됨에 따라, 전력 GaN FET는 사파이어로 제작된 GaN이나 대량 GaN보다 높은 효율성, 30V 이상의 DC-DC 전압 변환 공간에 적합한 형상 계수로 인해 더 많이 채택될 것이다.

여기서는 하드 변환 DC-DC 컨버터의 손실 메커니즘과 GaN FET 전력 단계 성능이 Si MOSFET보다 어떻게 우수한지 살펴보고, 80V GaN FET 전력 단계 및 80V Si 디바이스를 비교해본다.

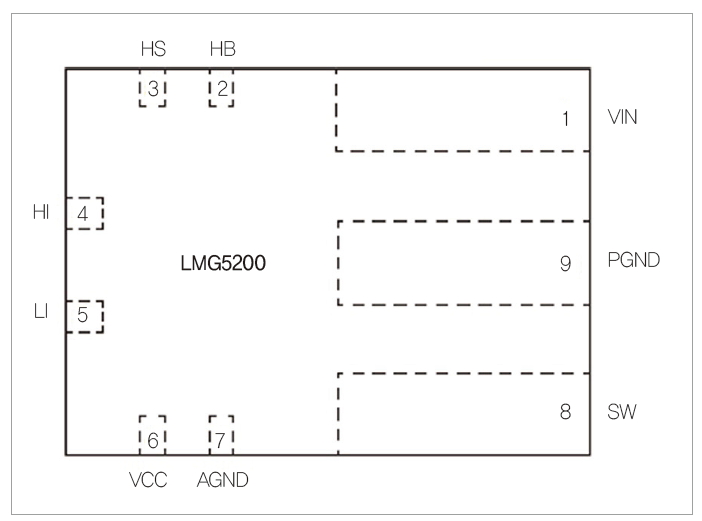

LMG5200과 같은 GaN FET 전력 단계 디바이스는 80V GaN 하프브리지 전력 모듈이다. 이 디바이스는 드라이버와 80V GaN FET 2개를 6mm×8mm QFN 패키지에 통합함에 따라 낮은 게이트 루프와 전력 루프 임피던스에 최적화되어 있다.[2] 입력은 3V CMOS와 호환 가능한 5V TTL 로직이다.

GaN은 과도한 게이트 전압을 견디지 못하므로 독점적인 클램핑 기법이 GaN FET의 게이트 전압을 항상 허용 한계 미만으로 유지한다. 또한 사용자 친화적이고 완제품에 배치 및 조립하기 쉬운 패키지로 제공되어 이산 GaN FET의 장점을 확장한다.

LMG5200은 언더필 없이도 IPC-2221B 및 IEC 60950 오염 등급 1 클리어런스 및 크립률을 충족시킨다. 그 이유는 고전압 및 저전압 핀 사이의 최소 간격이 0.5mm보다 크기 때문이다.

이로써 기판을 언더필로 제작하지 않아도 되고, 기판 설계를 크게 단순화할 수 있으며 비용도 절감할 수 있다. 배치용 전력 핀 사이의 간격이 적절하므로 핀아웃도 패드 내 설계 필요성을 없앤다. 또한 기판 복잡성과 비용을 줄이는 데에도 많은 도움이 된다(그림 1).

그림 1. GaN FET 전력 스테이지 디바이스의 상단도, 핀아웃 표시

DC-DC 컨버터 손실

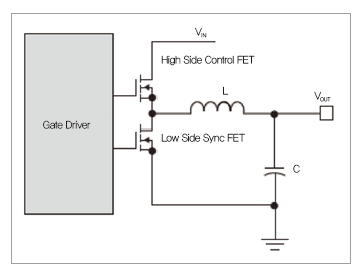

하드 변환 컨버터에서 손실을 일으키는 메커니즘에 대해 간단히 살펴보자. 여기서는 동기식 벅 컨버터(그림 2)를 DC-DC 컨버터로 사용해 하드 변환 컨버터의 손실을 비교한다. 손실 메커니즘 비교 방법은 다른 하드 변환 컨버터에도 적용할 수 있다.

그림 2. 벅 전력 스테이지의 계략도

변환 모드 컨버터의 손실은 크게 전도 손실과 스위칭 손실로 나눌 수 있다. 대부분의 하이사이드 MOSFET이 스위칭 손실을 없앤다.

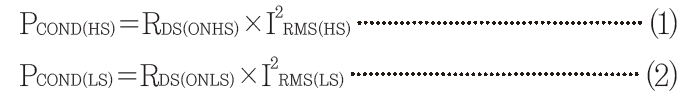

전도 손실은 사용률 함수이며 하이사이드 및 로사이드 디바이스 사이에 공유된다. 사용률이 낮은 DC-DC 컨버터의 경우, 로사이드 FET는 전도 손실이 높으며 다음과 같이 계산할 수 있다.

여기서 RDS(ONLS), RDS(ONHS)는 각각 로사이드 및 하이사이드 FET 저항이며 IRMS(LS), IRMS(HS)는 각각 로사이드 및 하이사이드 RMS 전류이다.

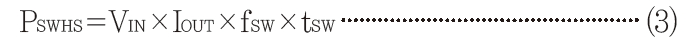

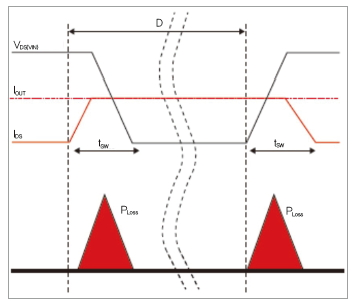

IDS 전류 및 VDS 중첩으로 인한 스위칭 손실(그림 3)은 벅 컨버터의 하이사이드에 있으며, 다음 식과 같이 추정할 수 있다.

여기서 tSW는 스위칭 시간이다. 여기에는 FET를 통한 정류 시간과 켜기/끄기 중 VIN별 FET의 드레인 투 소스 전압의 상승 및 하강 시간이 포함된다.

그림 3. 인덕티브 스위칭 중 켜기/끄기 손실

로사이드 FET는 ZVS(Zero Voltage Switching) 켜기/끄기에 의한 스위칭 손실이 없다. 인덕티브 스위칭의 실제 파형은 그림 3에 나타난 파형보다 훨씬 복잡하지만, 켜기/끄기에 사용된 스위칭 시간이 올바르다면 계산된 손실의 오류는 수용 가능하다.

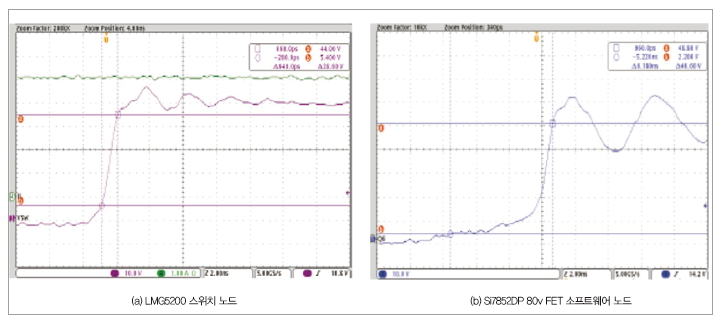

동일한 RDSON에 대한 작은 게이트 및 출력 커패시턴스 덕분에 GaN 디바이스 구조로 짧은 스위칭 시간이 가능해진다. 그림 4와 같이, GaN FET 전력 스테이지의 스위칭 시간은 파괴 전압이 비슷한 Si FET(Si7852DP)의 6ns에 비해 작은 1ns이다.

그림 4. GaN FET 전력 스테이지 스위치 노드와 실리콘 스위치 노드 전압의 파형 비교

스위칭 에지가 빠르다는 것은 Si MOSFET 기반의 벅 컨버터에 비해 Gan 모듈에서 스위칭 손실이 크게 감소한다는 것을 의미한다.

또한 매우 작은(300pH 미만) 전력 루프 인덕턴스 때문에 GaN FET 전력 스테이지 스위치 노드 파형에서 오버슈트가 미미하다. 게이트 루프와 공통 소스 인덕턴스도 GaN FET 전력 스테이지 패키지에서 최소화돼 200pH 미만이다. 이러한 루프의 높은 기생 인덕턴스는 막대한 전력 손실을 일으킬 수 있다.[3]

하이사이드 켜기/끄기 손실과 별도로 로사이드 MOSFET 바디 다이오드의 강제 정류는 고전압 DC-DC 컨버터의 중요한 스위칭 손실원이다.

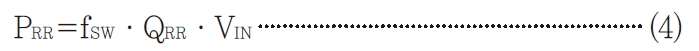

이러한 손실은 주로 프리휠링 로사이드 FET의 역회복 전하(QRR) 때문에 발생한다. 역회복에 의한 전력 손실은 다음과 같다.

GaN은 주요 캐리어 디바이스므로 역회복 기반 손실이 없다. 로사이드 MOSFET의 바디 다이오드는 데드 타임 중 전도된다.

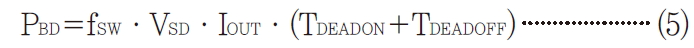

이와 같이 다이오드의 정방향 전압과 관련된 다이오드 전력 손실이 발생하게 된다.

Si FET의 3사분면 전도 전압이 최대 1V인 것에 비해, GaN은 더 높은 전도 전압을 갖는다(LMG5200의 경우 10A에서 VSD가 2V). 따라서 GaN 디바이스는 데드 타임 중 전력 손실이 크다. 이러한 손실을 최소화하기 위해서는 데드 타임이 작아야 한다.[4]

바디 다이오드와 관련된 전력 손실은 다음과 같이 계산할 수 있다.

MOSFET의 출력 커패시턴스에 저장된 에너지는 켜는 중 소멸된다. 출력 커패시턴스는 드레인투소스 전압의 강력한 함수이므로, 이와 같은 전력 손실 PCAP는 다음과 같이 계산한다.

여기서 QOSS(VIN)는 입력 전압에서 평가한 MOSFET의 출력 전하이다. GaN은 Si와 비교했을 때 같은 RDSON에 대한 출력 커패시턴스가 작으므로 PCAP 손실도 작다.

게이트 드라이버 손실은 스위칭 손실의 또 다른 원인이다. 게이트 드라이버와 관련된 손실에 대한 상세 설명은 LM5113 애플리케이션 보고서를 참조한다.[5]

또한 여기서 다루는 하드 변환 벅 컨버터의 활성 디바이스 관련 손실 이외에 인덕터와 관련된 손실도 존재한다. 이러한 손실은 철손(Core Loss)과 AC 및 DC 권선 손실(Winding Loss)을 포함하며 시스템 효율성을 계산할 때에도 고려해야 한다.[6, 7]

Si 비교 시 효율성 향상

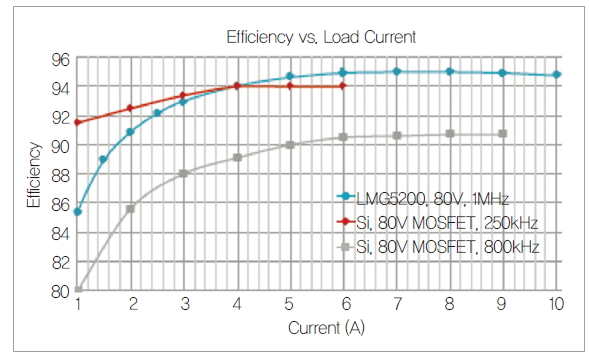

그림 5는 48V : 12V LMG5200 벅과 80v Si MOSFET 기반 벅 사이의 효율성 차이를 나타낸 것이다. LMG5200은 1MHz에서 스위칭하는 반면, Si 기반 디바이스는 각각 250kHz 및 800kHz에서 스위칭한다. LMG5200은 그림과 같이 낮은 주파수에서 스위칭하는 Si 솔루션보다 부하 대비 효율이 높다(1MHz : 800kHz). 이것은 GaN FET 전력 스테이지의 스위칭 및 전도 손실이 비슷한 등급의 Si MOSFET에 비해 훨씬 낮다는 것을 보여준다.

그림 5. 다른 주파수에서 LMG5200과 Si 비교

Si MOSFET 기반 컨버터를 250kHz 스위칭 주파수에 맞게 재설계한 경우, 예상과 같이 낮은 부하에서 Si 설계 효율이 높다. 하지만 부하가 4A로 증가하면 1MHz에서 스위칭하는 GaN FET 전력 스테이지의 효율이 훨씬 높다.

800kHz에서 Si 비교 시 GaN FET 전력 스테이지의 효율이 1MHz에서 스위칭해도 넓은 부하 범위에서 훨씬 높다.

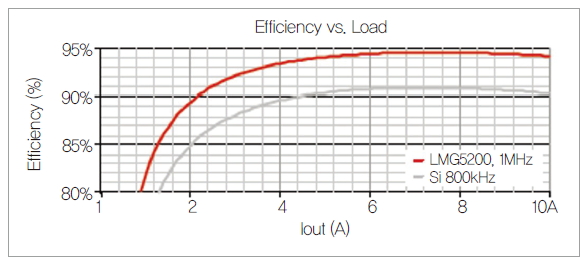

계산된 결과를 통해 하드 변환 벅에서 관찰한 효율을 비교하면, 사용한 단순화 모델의 오차 범위 내에 계산 결과가 있다는 것을 알 수 있다(그림 6).

그림 6. 1MHz의 GaN FET 전력 스테이지 설계와 800kHz의 Si FET 설계의 계산된 효율성 비교

전력 GaN FET는 낮은 게이트 전하 및 출력 커패시턴스로 인해 실리콘 FET보다 스위칭 손실을 크게 줄이고 효율을 향상시키면서 빠른 속도로 스위칭할 수 있다.

80V GaN FET 전력 스테이지인 LMG5200은 고효율 및/또는 작은 파형률이 필요한 애플리케이션에 최적화되어 있다. 이 고급 패키지는 재조성 및 기판 설계를 크게 단순화하며 비용을 절감시킨다.

또한 LMG5200은 다양한 애플리케이션의 성능을 개선하면서도 채택 위험을 줄일 수 있다. 이 애플리케이션에는 멀티 MHz 동기식 벅 컨버터, 오디오용 클래스 D 증폭기 및 데이터 통신, 텔레커뮤니케이션 서버용 48V-POL 컨버터가 포함돼 있다.

GaN FET 전력 스테이지 디바이스는 폭넓은 부하 범위에서 우수한 효율을 제공하면서 스위칭 주파수 및 전력 밀도를 개선한다.

그림 7. TI의 GaN 솔루션에 대해서는 www.ti.com/GaN을 참조한다

참고문헌

1. Lidow, A. Integrated Power Electronics Systems (CIPS), 2010 6th International Conference, 2010

2. LMG5200 datasheet

3. David Jauregui, Bo Wang, and Rengang Chen. Power Loss Calculation With Common Source Inductance Consideration for Synchronous Buck Converters, Application Report (SLPA009A), Texas Instruments, July 2011

4. Di Han; Sarlioglu, B. Wide Bandgap Power Devices and Applications (WiPDA), 2014 IEEE Workshop on DOI: 10.1109/WiPDA.2014.6964627

5. Narendra Mehta, Design Considerations for LM5113 Advanced GaN FET Driver During High-Frequency Operation, Application Report (SNVA723), Texas Instruments, November 2014

6. Reinert, J.; Brockmeyer, A.; De Doncker, R.W.A.A. Calculation of losses in ferro- and ferrimagnetic materials based on the modified Steinmetz equation, Industry Applications, IEEE Transactions on Volume: 37 , Issue: 4

7. Jieli Li; Abdallah, T.; Sullivan, C.R. Improved calculation of core loss with nonsinusoidal waveforms, Industry Applications Conference, 2001. Thirty-Sixth IAS Annual Meeting. Conference Record of the 2001 IEEE Volume: 4

Narendra Mehta _ 텍사스 인스트루먼트

Copyright ⓒ 첨단 & Hellot.net