[첨단 헬로티]

첨단 CMOS 스케일링 및 메모리 신기술의 도입으로 소자의 제작 과정과 구조가 점점 복잡해지고 있다. 메모리의 경우, 수직 스케일링의 도입으로 NAND 메모리 스택의 레이어 수가 늘어났고 이로 인해 스케일링 점유면적을 유지한 상태에서 계단식 콘택트 구조에 많은 레이어를 높은 종횡비(High Aspect Ratio)로 식각하는 것이 과제로 대두되었다. 독특한 집적 및 패턴 형성 기법을 사용해 스케일링 문제는 어느 정도 해결했지만, 이전에 없었던 새로운 설계 규칙상의 문제들이 발생되었다.

2차원 설계 규칙 검사(Design Rule Check, DRC)만으로는 목표 성능과 수율을 달성할 수 없다. 공정 특성 분석과 최적화에서도 실험계획법(Design of Experiment, DOE)에 의존할 수만은 없다. 지금까지는 레시피 개발 비용과 시간을 절약하기 위해 주로 DOE를 활용했지만, 엔지니어들이 방대한 양의 DOE에 의존해야 하는 상황에서는 막대한 공정 외 시간과 재료가 소모된다.

더구나, 강화된 프로세스 윈도우 조건과 공정 단계 간의 비직관적인 상호작용으로 제 1원리에 기초한 모델링 방식으로는 성능과 수율을 동시에 최적화하기 어려워졌다. 이런 상황에서 복잡한 공정 단계를 3D로 파악해야 하는 작업이 요구되고 있고, 가상제조 모델링 플랫폼인 Coventor SEMulator3D®가 이를 제공한다.

SEMulator3D로 가능해진 일들

이 소프트웨어는 일련의 단위 공정 단계에서 3D 디지털 프로세스 통합 모델을 통해 공정의 흐름을 재현한다. SEMulator3D는 완전히 통합된 공정 순서를 사용하여 각 공정 변화가 후속공정에 끼치는 영향을 예측한다. 만약 이러한 수단이 없다면, 팹에서 ‘제작-테스트’라는 긴 사이클을 거쳐야만 한다.

예를 들면, 엔지니어가 이 소프트웨어를 사용해 SAV(Self-Aligned Vias, 자기정렬 비아)로 TFMHM(Trench First Metal Hard Mask, 트렌치 퍼스트 금속 하드 마스크) BEOL(Back End of Line, 생산라인 후단)을 사용하는 RMG(Replacement Metal Gate, 대체 금속 게이트) FinFET을 신속하게 가상모델링 할 수 있다. 3D로 구조가 재현된 것을 확인 후, 2D 및 3D 구조에 대한 측정은 물론, 전기적 특성도 추출할 수 있다.

이 소프트웨어의 전기적 특성 분석 모듈은 저항 및 정전 용량 추출 기능도 갖추고 있어 공정과 디자인의 감도를 정확히 파악하는 데 도움이 된다. 결과적으로 단일 플랫폼에서 3D 모델링과 전기적 특성의 검증이 동시에 가능해 개발시간을 크게 단축시킬 수 있다. SEMulator3D의 공정 예측 모델과 상세한 실리콘 구조는 독립적인 솔버(solver)에서 사용하는 이상적인 기하학적 구조보다, 실제 제조상의 소자구조를 더 정확하게 반영해 완성도가 높다.

DRAM 모델 시연

SEMulator3D는 재료 선택비와 플럭스 분포 같은 소자의 전기적 특성 변화를 예측하는 기능을 통해, 가상제조(fabrication) 사례를 직관적으로 묘사한다. 아래의 간단한 DRAM 소자 사례에서는 목표로 세운 전기적 특성과 수율을 충족하는 데 필요한 게이트 식각 방법과 식각 단계의 특성을 파악할 수 있다.

해당 시연은 가상 제조에서 가장 일반적인 네 개의 작업 단계를 활용한다.

1.공정 흐름을 보정하고 소자 기술의 3D 구조를 예측하여 표현하는 표준 공정 설정.

2.구조 또는 전기적 특성의 적격성을 평가하는 관심 지표 추가.

지표에는 계측, 3D DRC, 전기적 특성 파라미터가 포함될 수 있음.

3.DOE와 보정을 이용한 설계 연구 설정.

4.감도 분석을 포함해 공정 구현 및/또는 설계 변경에 활용할 수 있는 데이터 분석.

표준 설정

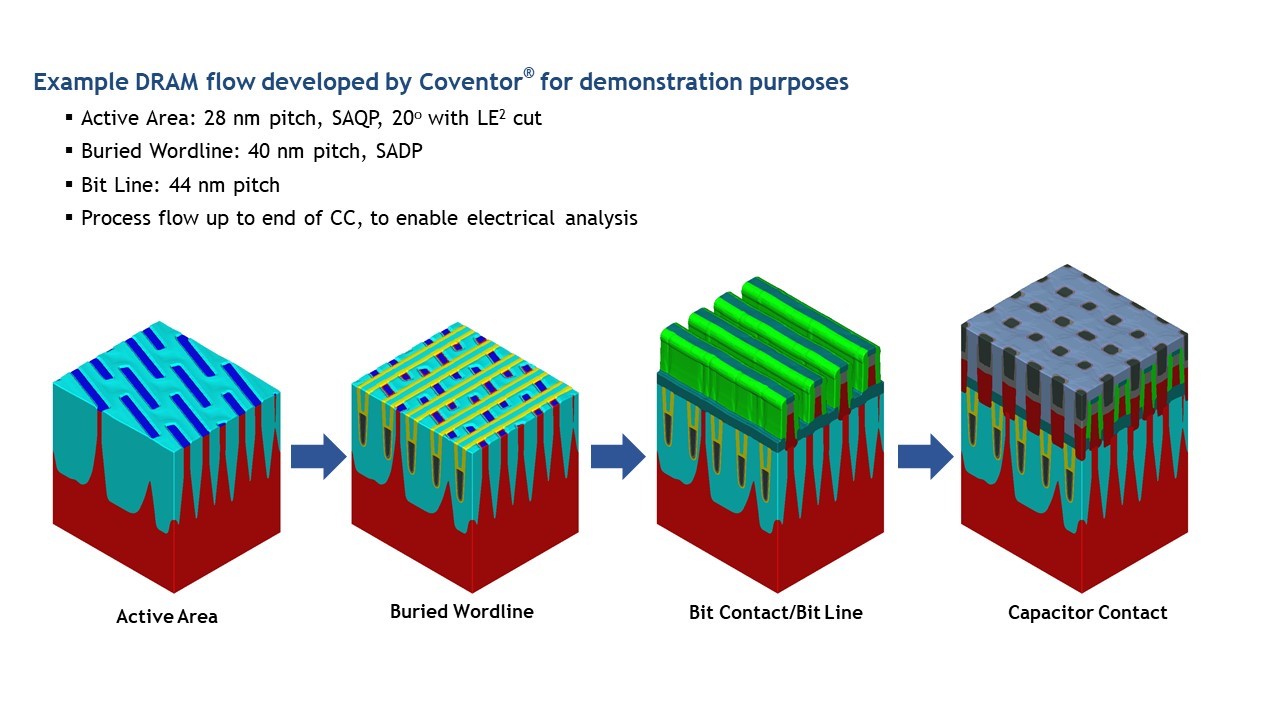

이 시연의 표준 설정 대상은 2X DRAM이다. 이 공정 흐름은 코벤터(Coventor)가 개발한 것으로 고객의 기밀정보를 사용하지 않았으며, 일반적으로 공개된 데이터를 기반으로 한다.

그림 1. 모델이 완성되면 그림과 같은 캐퍼시터 접촉부가 만들어진다. 이 지점에서 전기적 분석을 실시해 캐퍼시터의 모서리 효과를 조사할 수 있다.

이 시연에서 DRAM의 활성 영역(active area, AA)은 자가 정렬 쿼드러플 패터닝(self-aligned quadruple patterning, SAQP)과 20° 경사 LELE 또는 LE2(litho-etch-litho-etch, 2회 노광 후 식각) 절단을 사용할 때 피치가 28nm이다. 매립 워드 라인은 자가 정렬 더블 패터닝(self-aligned double patterning, SADP)을 사용할 때 피치가 40nm이며, 비트 라인은 SADP를 사용할 때 피치가 44nm이다. 가상 공정 플로우는 전기적 특성의 분석이 가능한 지점인 캐퍼시터 접촉부(capacitor contact, CC) 형성에 도달 후 끝나는데, 여기서 캐퍼시터의 모서리 효과를 분석할 수 있다.

관심 지표 추가

공정 단계별로 이해와 보정이 쉬운 기하학적·물리적 파라미터를 입력해야 한다. 다음 단계는 작업 플로우에서 관심 지표를 식별하는 것이다. 실제 팹에서와 마찬가지로, 증착 균일성, 식각 비등방성(anisotropy), 선택비(selectivity) 같은 단위 공정 파라미터들이, 상호간 또는 설계디자인과 복잡한 상호작용을 통해 최종 소자 구조에 영향을 끼친다.

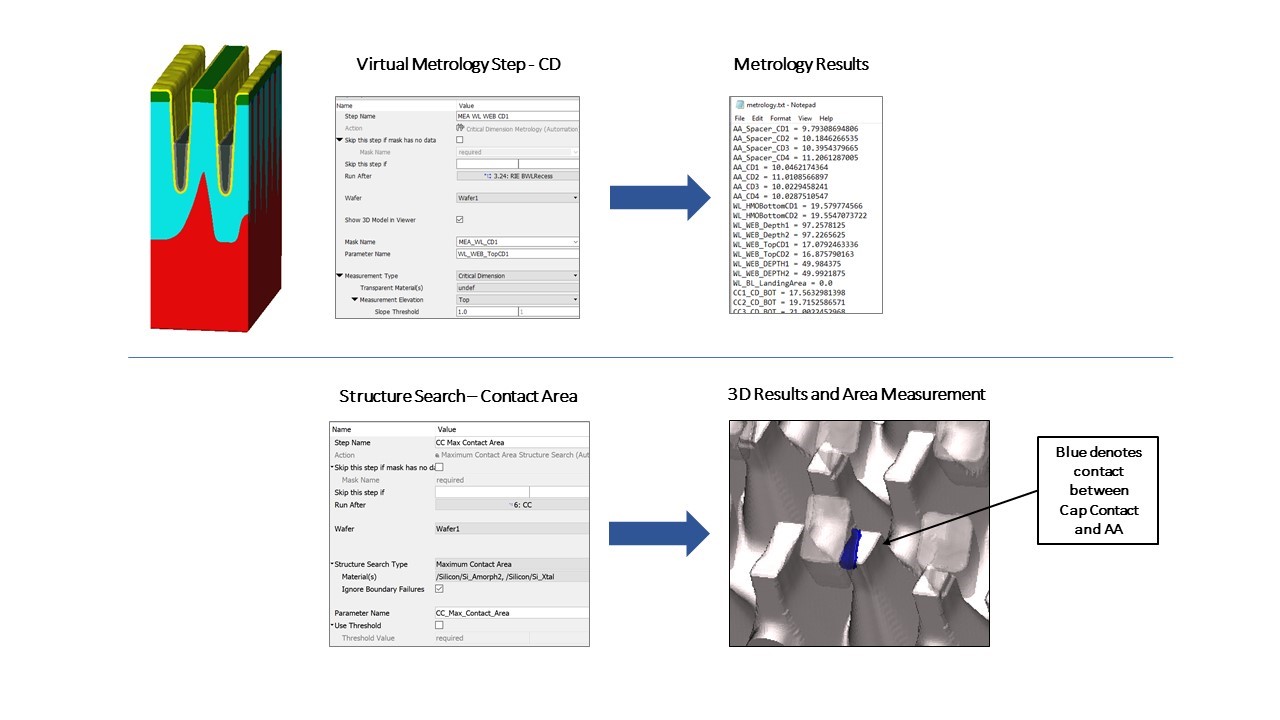

그림 2. 가상 계측(왼쪽)을 통해 CD, 식각 깊이, 박막 두께 같은 구조를 쉽게 측정한다. 구조 검색 (오른쪽)을 통해 측정 최대/최소치를 확인하고, 도체 소재의 구성 요소를 계산해 네트의 단락 또는 단선을 확인한다.

SEMulator3D를 시용한 기하학적 계측에는 두 가지 방법이 있다. 하나는 가상 계측으로, 모델 구조를 측정하여 피쳐(feature)가 기대 값에 맞는지 확인하는 것이다. 또 하나는 구조 검색으로, 전체 3D 모델이나 또는 그 일부 영역을 검사해서 최대/최소 측정치를 확인하고, 박막 두께나 라인 너비 및 접촉 면적 등의 값들과 그 위치를 도출한다. 또한, 도체 소재의 구성 요소의 수를 계산해 전기 네트(electrical net) 단락(shorts) 또는 단선(opens) 여부를 쉽게 확인할 수 있다(그림 2).

구조 검색은 공정 변수의 변화에 따라 기하학적 위치와 형상의 변화가 발생할 경우에 특히 유용하다. 예를 들어, 그림 2는 CC와 AA 간의 경계접촉 면적을 보여준다. 결과에서 강조된 부분들은 소자의 문제점들이 검출된 경우다.

소자전기적 특성 시뮬레이션 Electrical Device Simulation

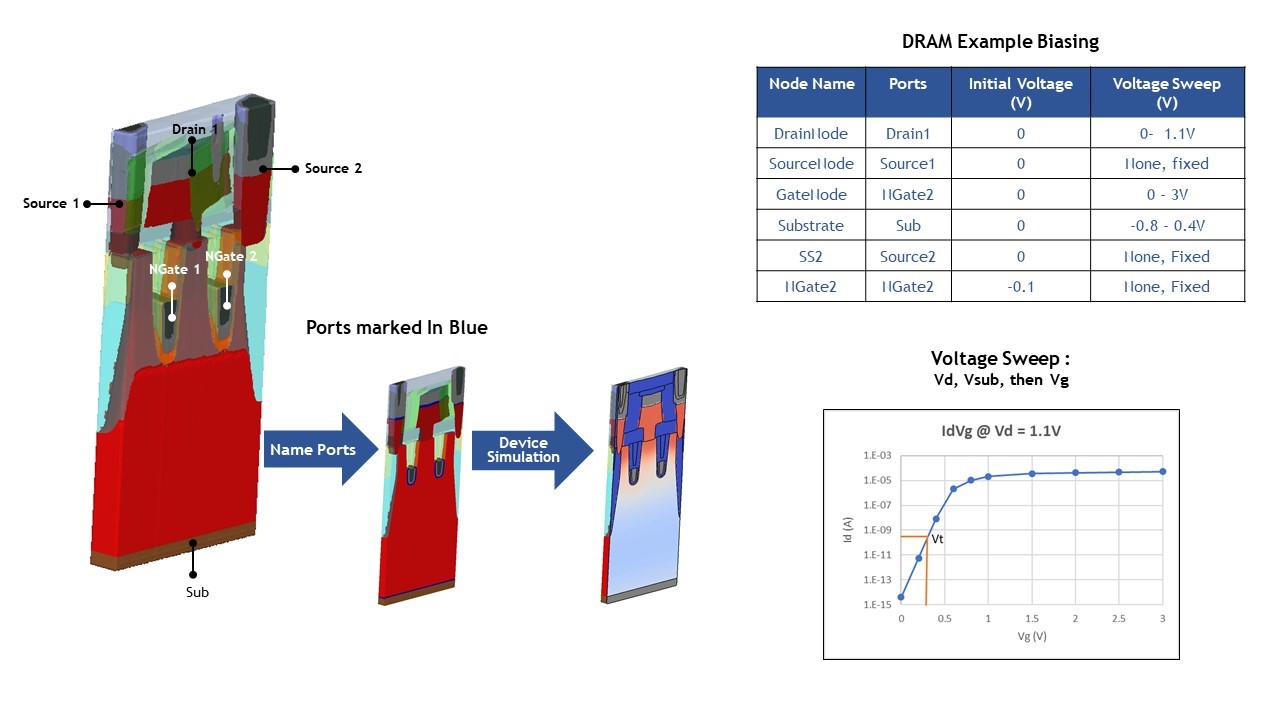

그림 3. SEMulator3D는 3D소자구조내의 전극을 식별해 소자의 전기적 특성을 시뮬레이션한다. 그러나 기존의 TCAD 모델링처럼 오랜 시간이 소요되지 않는다.

소자전기적 특성 시뮬레이션을 사용해 다른 종류의 지표를 추출할 수 있다. 그림 2의 모델구조를 사용해, 전기적 특성 시뮬레이션까지 수행할 수 있다.

소프트웨어는 3D구조내의 소자의 전극을 식별하여 온도, 밴드갭, 전자·정공 이동도(hole mobility) 같은 변수로 소자 특성을 시뮬레이션한다. 노드(핀 하나 또는 서로 묶여 있는 여러 핀)의 수동 식별과 자동 식별이 모두 가능해 초기 전압이나 전류를 일부 노드의 전압 스윕(voltage sweep)과 함께 설정할 수 있다.

그림 3의 전기 시뮬레이션은 게이트 2개, 소스 2개, 드레인 1개, 기판 1개를 나타낸다. 엔지니어는 DRAM 예시 바이어싱 표에서 볼 수 있는 전압 스윕 뿐 아니라 바이어스 또는 초기 고정 전압도 자유롭게 설정할 수 있다.

또한 문턱전압(threshold voltage, Vth), 문턱전압 이하의 기울기(sub-threshold slope, SS), 드레인 유도 장벽 감소(drain-induced barrier lowering, DIBL), 각 전압에서의 ON 전류(ION) 같은 관심 지표를 자동으로 추출할 수 있다. 시간이 많이 걸리는 정밀한 TCAD 모델링 수단 없이도, 3D 공정이 전기 성능에 미치는 영향을 바로 확인할 수 있다.

기하학적 구조 변화의 영향

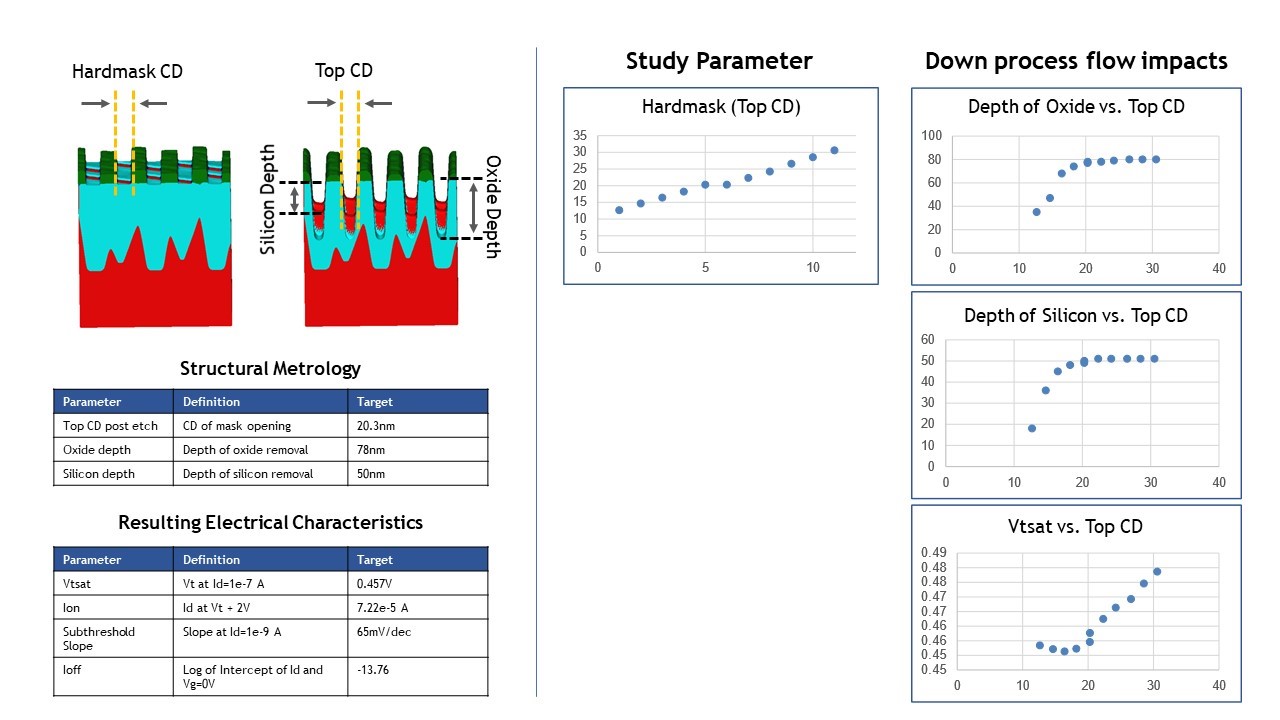

기하학적 구조 변화에 따른 영향에 대한 설계 연구는 하드마스크 CD/상단 CD, 실리콘 깊이, 산화물의 깊이 등의 타겟이 사전에 설정된 표준모델을 먼저 조사하는 것으로 시작한다. SEMulator3D는 Vt, ION, IOFF, SS등의 수치를 활용하여 전기적 특성을 추출한다(그림 4, 왼쪽).

그림 4. 기하학적 구조 변화의 영향을 연구하는 표준 모델(왼쪽). SEMulator3D(오른쪽)를 사용한 실험에 따르면, 20nm 근방으로부터 산화물 깊이와 실리콘 깊이의 CD 변화에 대한 감도는 감소하지만, Vtsat 감도는 증가하는 것으로 확인된다.

이 연구의 목적은 그림 4의 하드마스크 CD를 12nm부터 2nm씩 늘려가며 30nm까지 변화를 주며, 실리콘 깊이와 산화물과 같은 다른 구조 파라미터를 모니터링하는 것이다. 플로우 초기의 공정 단계에 이러한 변화를 주면 후속 공정 단계에서의 모델이 어떻게 변화할 지를 예측할 수 있다.

그림 4(오른쪽)는 하드마스크 CD 변화에 의해 게이트 식각 이후가 비선형적으로 반응하는 것을 나타낸 것이다. 산화물 깊이와 상단 실리콘 깊이는 작은 CD범위에서는 상단 CD에 민감하지만, 큰 CD범위에서는 포화된다. 반면 Vtsat은 표준값 20nm을 초과한 범위에서도 CD 변화에 따라 크게 증가한다. 따라서 SEMulator3D의 지표를 이용하면, 하나의 기하학적 구조 변화가 유도하는 다양한 후속반응을 볼 수 있어, 다른 파라미터에 대해 미치는 영향도 조사할 수 있다.

중요한 공정스텝을 식별하기

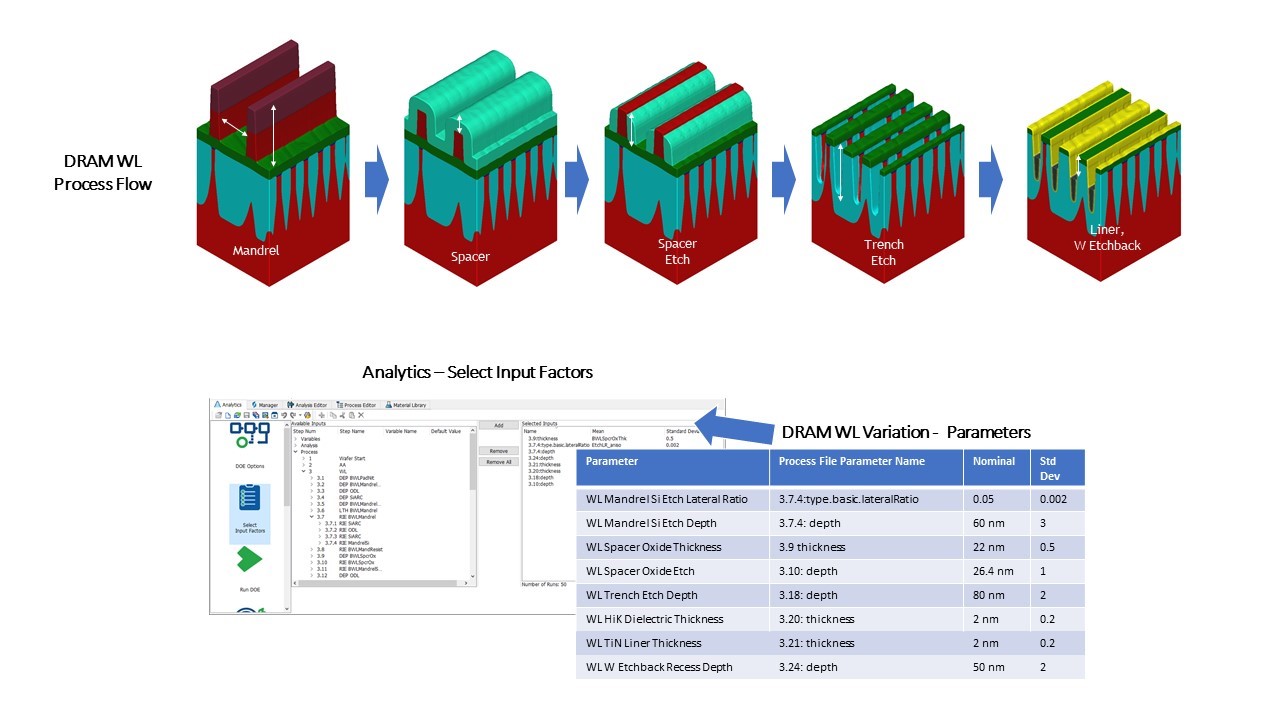

다음은 몬테 카를로 변수 연구(Monte Carlo variation study)로 이루어진 DOE를 실시해 중요 공정 단계를 식별하는 단계다(그림 5). 파라미터 변화 연구에서는 몬테 카를로를 이용한 DRAM 워드 라인(WL) 변화가 사용된다.

그림 5. SEMulator3D는 수백 또는 수천개에 이르는 DOE 실행에 의한 회귀분석을 사용해 특정 메트릭에 영향을 미치는 주요 프로세스 파라메터를 식별한다.

WL 공정 파라미터 값은 평균값 또는 표준값과 표준편차를 중심으로 하는 가우스 분포(Gaussian distribution)에 따라 무작위로 설정된다. 시연으로 50개 실험이 선택되었다. 그러나 보통 유의미한 연구를 위해서는 100개 이상의 실험이 필요하다고 여겨진다.

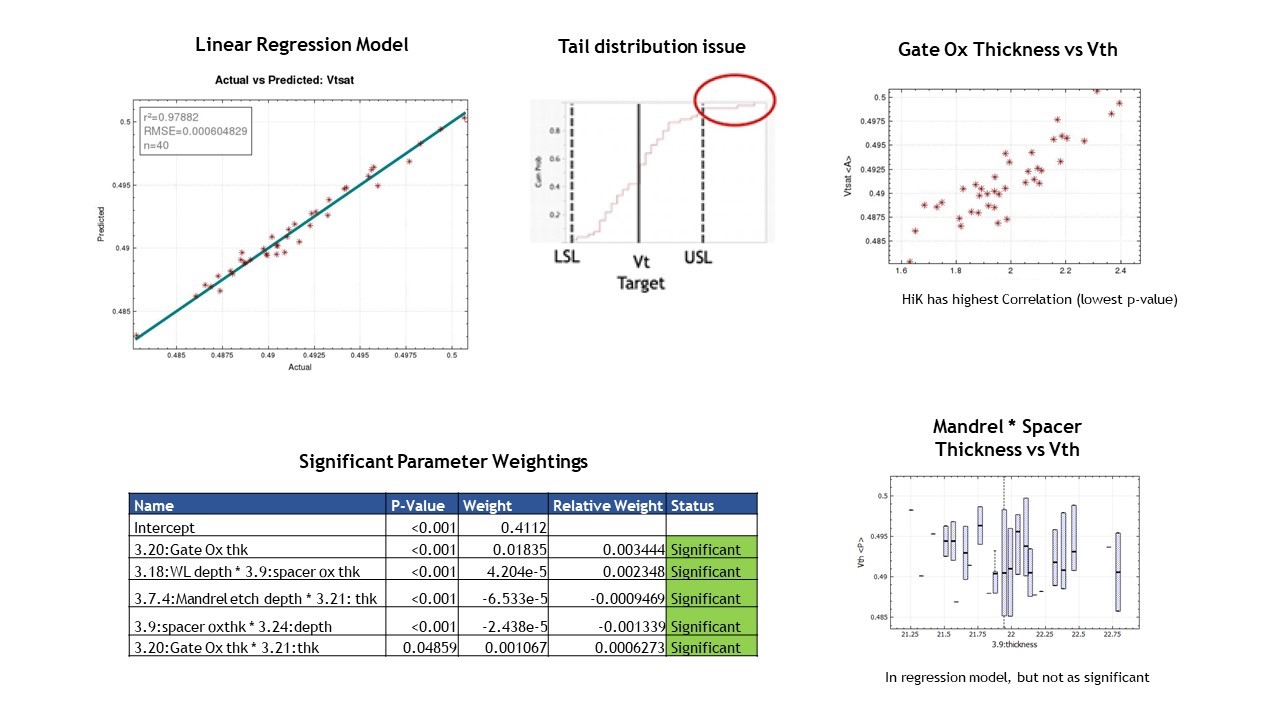

그림6은 DOE 결과다. DOE 실행에서 문턱전압(Vt)의 변화폭은 0.4837V와 0.5031V 사이이다. SEMulator3D의 회귀분석에 의해 문턱전압에 미치는 영향 측면에서 중요하다고 판단되는 다섯 가지 파라미터를 식별한다(이들 파라미터의 p 값은 귀무가설(null hypothesis)이 배제되는 0.05 미만). 첫째 파라미터인 절편(intercept)은 항상 이 리스트에 포함되므로 이 논의에서는 제외한다.

그림 6. SEMulator3D에서 계측을 분석하여 중요 파라미터를 규명하고, 위와 같은 코너 케이스(빨간색 동그라미)를 밝혀낼 수 있다.

이 실험에서 정밀조사가 추가로 필요하다고 확인된 주요 인자 다섯 가지는 다음과 같다.

•게이트 유전체 두께 (가장 중요하다고 판단되는 파라미터)

•워드 라인 식각과 스페이서 두께의 교차항

•맨드릴 식각 깊이와 게이트 두께의 교차항

•스페이서 산화물 두께와 연마 두께의 교차항

•게이트 유전체 두께와 스페이서 두께의 교차항

선형 회귀 그래프에서 결정계수가 높은 값(r2) 0.97882는 이 모델이 데이터와 잘 맞는다는 뜻이다. 게이트 산화물 두께 대 Vth의 그래프에서 상관관계는 크다고 볼 수 있지만, 맨드릴 스페이서 두께 대 Vth 표에서는 크지 않아 중요 입력인자 후보에서 제외해도 된다고 볼 수 있다.

DOE 결과를 통해 Vth의 규격 하한(Lower Spec Limit, LSL)에서 규격 상한(Upper Spec Limit, USL) 범위에서 벗어나는 코너 케이스를 쉽게 확인할 수 있으며, 엔지니어는 이를 면밀히 조사해, 규격에서 벗어난 원인이 된 공정 조건을 찾을 수 있다.

공정 최적화

최적화의 또 다른 관점으로, 전기 특성을 지표로 사용할 수 있다. 이를 통해 공정 단계의 최적화를 목표로 세울 수 있다. 각 공정 단계의 파라미터를 변화시켜 전기적 성능을 만족시킬 수 있는 조건을 찾을 수 있다.

소프트웨어에서 사용 장비에 따른 식각 행동 별 허용 범위를 정의할 수 있다. 즉, 재료 식각 선택비, 측면 비율, 중합·테이퍼, 스퍼터링 및 이온 플럭스 분포 같은 파라미터의 식각 행동을 정의할 수 있다. DOE를 통해 식별된 중요 입력 요소를 활용해, 전기적 성능의 목표치를 입력할 수 있다.

SEMulator3D는 직접 최적화를 통해 이러한 전기적 특성 목표치가 충족되도록 WL 식각에 가장 적합한 식각 단계의 행동 프로세스 파라미터를 결정한다. 보정을 거친 공정 제안에는 산화물, 실리콘, 질화물(nitride) 비율, 산화물 및 실리콘 테이퍼, 선택비, 측벽 각도 같은 파라미터가 포함된다.

이를 통해, 해당 공정 연구 범위 내에서 목표의 전기적 성능이 달성될 수 있는지 없는지의 여부를 확인할 수 있다.

가상 공정으로 비용과 시간을 절감

개발 초기 단계와 하드웨어 구현 전에는 다양한 공정 상의 가정들이 세워진다. 가상 공정과 제조를 이용한다면 실제 웨이퍼 작업에 드는 시간과 비용 없이도 이러한 가정들을 검증할 수 있다.

위의 DRAM 연구 사례가 보여주듯 가상 환경에서의 DOE 및 공정 변화 실험을 통해, 관련이 없는 DOE로 인한 시간과 비용의 낭비를 없애고, 성능과 수율 목표를 신속하게 달성해, 결과적으로 제품화까지의 시간이 단축될 수 있다.

글 / 조셉 어빈 램리서치 반도체 공정 및 통합 부문 디렉터 (Joseph Ervin, Director, Semiconductor Process and Integration, Lam Research)