테크노트 “기존 회로 대비 반도체 칩의 전력 소모 크게 줄여”

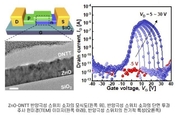

포스텍 이병훈 교수팀, 반양극성 스위치 신소자 이용해 삼진 회로 구현 매일 꼭 한 번은 충전해야 하는 휴대전화. 이는 휴대전화의 기능이 고도로 발달하면서 소모되는 전력량 역시 늘어난 탓이다. 휴대전화 뿐만 아니라 클라우드 데이터센터, 슈퍼컴퓨터 등 막대한 데이터를 처리하기 위해선 이에 상응하는 전력이 필요하다. 최근 국내 연구팀은 이처럼 기하급수적으로 늘어나는 반도체 칩의 전력 소모를 줄일 가능성을 열었다. 포항공과대학(포스텍)은 전자전기공학과 이병훈·강석형 교수· 박사과정 이용수 씨 연구팀이 적은 전력으로도 우수한 성능을 보이는 삼진 로직 회로(Ternary logic circuit)에 필요한 원천소자기술을 개발하는 데 성공했다고 밝혔다. 이 연구성과는 국제 학술지 ‘ACS 나노(ACS Nano)’에 최근 게재됐다. 삼진 로직 회로는 0과 1로 동작하는 기존의 이진 회로와 달리, 0, 1, 2로 동작하는 회로다. 처리할 수 있는 정보의 양이 늘어날 뿐만 아니라, 이진 회로보다 필요한 소자 수가 적어 전력 소모 또한 줄어들 것으로 여겨졌다. 다만, 회로의 구조적인 문제로 정보처리 과정에서 누설전류가 생겨 실제로는 여전히 전력 소모가 컸다. 연구팀은 특정 전압