ESD 이슈를 중심으로 한 전자산업 기술변화

반도체 소자 기술은 가히 한계에 다다르고 있다고 해도 과언이 아닐 정도로 급격히 변화하고 있다. 양산 소자는 14nm에 이르며, 최근 IBM은 7nm 이상의 기술 집적도를 가진 소자 테스트에 성공한 바 있다(그림 1)1).

그림 1. 현재 양산 소자는 14nm에 이른다.

이처럼 빠른 기술의 변화를 통해 새로운 제품과 기술이 등장하고 있지만, 이러한 신기술 소자를 다루는 표면실장 산업은 아직 준비되지 않은 것처럼 보인다.

대부분의 기업에서는 아직도 정전기 관리가 제대로 이루어지고 있지 않다. 많은 기업이 정전기 접지와 일반 설비 접지 기준을 구분하지 못하며, 국제 표준에서 요구하는 관리 방법, 절차 및 교육 등의 요구사항과 격차가 상당히 큰 편이다. 필자는 전반적인 산업 환경과 업무 추진 문화 모두 포괄적으로 변화되어야 한다고 생각한다.

반도체 소자 기술의 발전은 단순히 기술 집적도(Techno-logy Node)가 증가한 것이 아니며, 소자에 사용된 재료 및 Package가 다양화되고 고집적화 된다는 것이 가장 큰 특징이다. 이러한 기술적 고집적화는 소자의 프로세스 처리 속도를 더욱 빠르게 한다는 특징이 있다.

최근 고속 처리 속도를 갖는 소자는 수 GHz 대역에 이른다. 이런 고속 처리 속도를 갖는 소자는 내부 회로의 물리적인 간격이 기술 집적도에 따라 아주 작아졌다는 것을 의미하며, 그와 동시에 소자의 ESD 민감도가 증가되었음을 의미한다. 다시 말해, 초고속 소자를 사용하는 최신 소자의 경우, ESD 민감도가 증가하여 표면실장 작업 중의 ESD 제어가 전보다 훨씬 중요해 졌다는 것이다.

이는 전보다 더 높은 수준의 ESD 제어와 기술 변화에 따른 제어 교육 및 훈련이 회사 전반에 필요하다는 뜻이기도 하다. 더불어 소자의 패키지가 커지면 EMC Mold가 함께 커지고 소자의 Capacitance 또한 증가하게 된다. 이러한 상황에서, 동일한 Die를 다른 크기의 Package로 조립한다면 전혀 다른 CDM 민감도를 갖게 되고, 그에 따른 ESD 제어 수준은 완전히 달라지게 된다.

한국뿐만이 아닌 전세계 대부분의 SMT 기업은 이러한 변화를 민감하게 받아들이지 않고 있는 것처럼 보인다. 하지만 스마트폰 제조 기업에게는 특히 아주 민감하면서도 큰 이슈로 다루어지고 있다.

한편 자동차 전장 산업에서는 오랜 기간 동안 ESD 산업에서 선도적인 역할을 해 왔다.

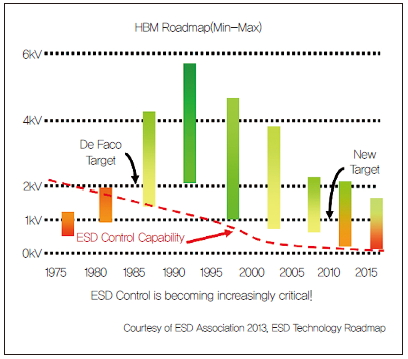

자동차 산업에서는 1980년대 초반에 최초로 소자의 Device Passing Level을 HBM 2kV와 MM 200V로 규정지었고, 이는 반도체 산업 전반에 폭 넓게 받아들여져 산업 불문율로 자리 잡기도 했다(그림 2).

그림 2. HBM 로드맵

소자 기술 변화에 따른 ESD 제어 흐름 변화

오랜 기간 유지되던 반도체 소자의 Passing Level은 2000년대 중반을 지나면서 벽에 부딪히기 시작했다. 기존의 2kV HBM에 맞춰 생산하면 시장이 요구하는 기한 내에 모든 소자를 생산하기 어려워지게 됐고, 이에 MM 테스트 필요성에 대한 논의가 이루어졌다.

수많은 반도체 회사와 전자 업체 관계자들, 그리고 저명한 컨설턴트가 함께 이러한 상황에 입각하여 ESD Industry Council을 구성하게 되었고, 오랜 회의를 통해 종전에 사용하던 2kV HBM ESD Passing Level을 1kV HBM으로 합의하게 됐다. 이와 함께 MM테스트는 더 이상 진행하지 않기로 했다. 아울러 동시에 진행되던 CDM 설계 수준은 500V에서 250V로 낮아지게 됐다.

이처럼 진행될 수 있었던 가장 큰 동기는 대부분의 전자 업체에서 반도체 소자를 취급할 때에 최소한의 HBM 제어를 적절히 진행하고 있었다. 또한 이 경우 1kV이상의 HBM설계가 되어있는 소자의 경우 대부분 안전하게 취급이 가능했으며, 이러한 변화에 따른 위험이 크지 않았기 때문이다. 이러한 결론은 수십억 개의 소자 불량 데이터를 근거로 했다.

한편, 급격히 진화하는 반도체 기술과, 그에 따른 보호회로의 약화는 표면실장 제조 현장에서 새로운 제품 품질 문제와 신뢰성 문제로 대두되고 있다. 사실, 이는 소자 업체의 책임 떠넘기기로만 볼 수 없다. 그 이유는 필자가 돌이켜 볼 때, 지난 20년간 한국 전자 산업 전반에 걸쳐 ESD에 대한 이해가 충분하지 못했고, 이로 인한 부작용으로 보일 수 있는 부분도 상당했기 때문이다. 결국 ESD 제어 산업 구조가 적절하지 못하고, 적절한 수준의 교육이 부재했기 때문이기도 하다.

소수의 ESD 관련 업체에 의한 솔루션 판매 위주로 산업이 지나치게 상업화되어 기술적인 근거와 타당성보다 판매 네트워크 위주의 시장 형성 또한 문제이다. 더불어 ESD 업무 특성상 대학과 같은 체계적인 교육이 뒷받침되지 못했으며, 그 결과 관련 업체의 마케팅 정보에 지나치게 의존했던 것도 문제이다.

그 뿐만 아니라, 전자 제조업체 엔지니어의 전문성 부족도 이러한 미숙한 산업 현장을 방조해 왔다고 하지 않을 수 없다. 엔지니어적인 연구·분석 없이, ‘빨리 빨리’해야 한다는 문화가 기술 분야에서도 그대로 적용된 산업 현장의 분위기 또한 문제이다.

기업 전반의 품질과 신뢰성에 대한 인식은 여전히 부족해 보인다. 이에 대해서는 엔지니어에 대한 체계적인 교육을 제공하지 못하는 점이 문제이다. 정전기 문제를 지나치게 미스터리하게만 생각한 결과, 많은 부분 사실임에도 불구하고 원인을 알 수 없는 불량에 대하여 정전기 문제로 치부해 온 경향이 있다. 이러한 점이 실제 정전기 문제를 만났을 때에 부정적인 대응을 하도록 했을 수도 있다. 산업 전반에서 반성의 시간이 필요하다.

물론, 최근 들어 고객과 소비자의 요구가 높아지면서 전자 산업 전반에서 제품의 품질과 신뢰성 인식이 높아진 것도 사실이다. 이는 앞서 설명한 바와 같이, 신기술이 적용된 소자들로 인한 ESD 문제도 급증했기 때문인 것으로 보인다.

ESD 민감도 변화 : HBM, MM & CDM 업데이트

산업계에서 가장 크게 변화된 부분 중의 하나로, ESD Industry Council에 의한 HBM, CDM Level변화와 MM 표준의 Downgrade를 꼽을 수 있다. 앞서 설명한 바와 같이 HBM Level은 2kV에서 1kV로 낮게 제안 됐고, 이는 반도체 업계 전반에 빠르게 흡수 됐다. 이에 따라 전자 업계에서도 이를 대폭 수용하고 있는 추세이다.

사실, 이에 따른 소자 불량율의 변화는 거의 없다고 보는 것이 좋다. 하지만 이렇게 권장하는 이유는 500V 정도의 설계 소자의 경우, 인체접지와 접지된 작업대, 그리고 ESD 포장재 사용과 같은 아주 간단한 HBM 제어 방법만으로도 유효한 제어가 가능하기 때문이다2).

MM(Machine Model)의 경우는 상황이 상당히 다르다. MM은 일본에서 Toshiba를 중심으로 낮은 전압의 HBM Stress를 모델로 하여(HBM의 Worst Case Scenario) 시작된 machine model이 AEC와 JEDEC 등에서 받아들여지면서 Machine Model로 자리 잡게 됐다.

여러 표준에서 언급하고 있는 바와 같이 HBM과 MM은 서로 Correlation관계를 갖고 있으며, 적게는 5% 내지는 많을 때에는 20% 정도의 빈도로 동시에 발생한다3). 이와 같은 이유로, HBM 보호회로 설계는 MM 방전도 동시에 보호한다. 사실, MM 테스트를 계속한다면 낮은 수준의 MM 방전을 제어하기 위해 ESD 보호회로 설계를 개선해야 한다. 이 때문에 MM 표준이 Downgrade되기도 했고, 언어적인 표현의 오해로 인해 MM 표준을 제거하기도 했다.

CDM Level의 경우에 내용은 조금 다르지만, 기존의 500V에서 250V로 대폭 낮아졌다. CDM 불량도 다른 모델과 마찬가지로 기준 하향 조정과 함께 더욱 까다로운 문제가 되고 있다.

하지만 여러 반도체 회사의 발표를 기준으로 볼 때, CDM은 HBM에 비해 덜 익숙하고 잘 제어지 않아 대부분의 ESD 불량 원인으로 손꼽히고 있다. 사실, 500V에서 250V로 낮춘 것도 원인이겠지만, 대부분의 표면실장 및 전자 회사에서 사용하고 있는 부도체가 가장 중요한 원인이라고 할 수 있다.

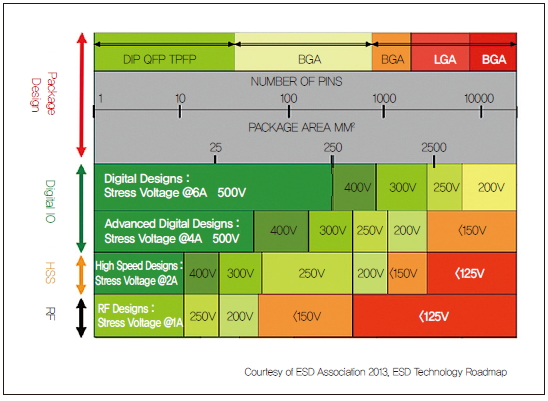

뿐만 아니라 CDM의 경우는, 소자의 Package 형태가 많이 변경되는 것 또한 중요한 원인으로 작용했다. DIP Type의 소자는 I/O Pin수가 상대적으로 많지 않고 동작 속도도 빠르지 않았다. 그런 소자의 Die를 BGA화하면 Package의 크기가 커지고, I/O Pin의 수가 증가하며, 동작 속도까지 빠르게 유지할 수 있다. 이때 소자의 CDM 민감도 또한 함께 증가한 것이다. 그림 3은 ESD Association에서 소개하고 있는 ESD Roadmap 중에서 소자의 Package별 CDM 민감도 분포를 정리한 내용이다.

그림 3. ESD Association에서 소개하고 있는 ESD Roadmap 중에서 소자의 Package별 CDM 민감도 분포.

ANSI/ESD S20.20 & IEC-61340-5-1

사실, 앞서 설명한 바와 같이 반도체 소자의 급격한 기술 변화에 따라 소자의 동작 전압이 낮아졌고, 이에 따른 Leakage 민감도가 증가했다. 이는 ESD 관리 제어와 아주 직접적인 관련을 갖는다. 아주 작은 변화에도 소자의 민감도가 변하게 된 것이다. 이 같은 주요한 변화는 ANSI/ESD S20.20과 IEC-61340-5-1 등 널리 받아들여지고 있는 국제 표준에서도 마찬가지다.

1999년에 처음 작성된 ANSI/ESD S20.20 표준은 HBM 100V이상의 민감도를 가진 소자 제어 사용을 목적으로 제작됐으며, 이후 전 세계적으로 ESD 제어 표준으로 퍼지게 됐다.

또한 유럽을 중심으로 하는 ESD 제어문서는 2002년에 작성된 IEC-61340-5-1이며, S20.20과 같이 HBM 100V 이상을 목표로 하고 있다. 두 문서는 쌍둥이 문서로서, 하나는 북미를 중심으로 한 ANSI(American National Standard Institute) 체계이고, 하나는 유럽을 중심으로 한 IEC 체계이다. 한국은 IEC 회원국으로 활동하고 있다. 두 문서는 동일한 Scope를 갖으며 내용 또한 대부분 동일하다. 우리가 관습적으로 알고 있는 정전기 100V관리는 사실, 이 두 문서를 기반으로 널리 전달되어졌다고 볼 수 있다. 대부분의 내용은 인체 접지 방법과 바닥, 제전화, 제전복, 의자 등과 같이 인체 대전 제어 관련 HBM 제어 요소들로 구성되어 있다. ANSI/ESD S20.20과 IEC-61340-5-1문서는 2007년, 같은 해에 개정이 이루어졌다.

이후 2009년부터 시작된 약 5년간의 Revision 작업을 거친 결과, 2014년에 Update된 문서로 거듭나게 됐다. 그 결과 ANSI/ESD S20.20-2014의 Scope는 HBM 100V, CDM 200V, 그리고 MM 대신 절연된 도체 35V로 설정되는 등 많은 부분의 변경이 이루어졌다. IEC 61340-5-1문서 또한 현재 S20.20에서 개정된 내용에 따라 변경 작업이 이루어지고 있으며, 2016년 봄에 개정 작업이 완료될 예정이다.

자동차 산업과 FPD, LED 산업

자동차 산업과 평판디스플레이 산업, 그리고 LED 산업 분야 또한 정리해야할 이슈가 많다. 자동차 산업의 경우, 국제 표준과 너무나 상이한 ESD 관리 방법이 만연해 있다. 이를 시정하려는 노력에 비해 잘못된 관습에 젖어 변화를 거부하거나, 변화에 민감하지 않은 모습을 볼 때가 많아 답답할 때가 많다. 다음 기회에 설명 하겠지만, CBE(Charge Board Event)와 같은 ESD 현상이 플라스틱 사출물과 결합된 PCB의 제조 및 조립 공정에서 많은 문제를 야기하고 있으며, 이에 대한 공감대 형성 및 개선, 관리 방안에 대한 산업계 전반의 정확한 이해와 정보 교류가 절실하다.

평판 디스플레이 산업도 유사하다. 반도체 소자와 달리 FPD 소자는 ESD 민감도 수준을 측정할 수 있는 합의된 방법이나 표준이 존재하지 않는다. 최첨단을 자랑하는 FPD 산업에서 불량을 일으키는 소자의 제어 기준이 엔지니어의 주관적인 판단에 근거하여 수립되고 있는 현실이 너무나 안타깝다.

LED 산업 또한 유사하지만, 평판디스플레이와는 다르게 LED 소자의 I/O에 대해서는 HBM 테스트를 진행하고 있다. 하지만 CDM테스트는 실시되지 않고 있다고 한다. 또한 소자의 사양서에도 표기하지 않으며 CDM에 대한 품질 보증도 하지 않는다.

HBM의 경우에도 Zener Diode를 사용하여 방전 펄스를 제어하고 있으나, CDM의 경우에는 보호 효과가 같지 않다. Zener Diode의 경우에는 Clamping Voltage와 Response Time에 따라서 방전 제어 효과가 달라질 수 있다.

마무리

ESD 분야에서 세계적인 변화의 흐름에 한국기업과 엔지니어의 참여는 아직 저조한 편이다. 기업의 비즈니스는 글로벌하게 진행되지만, 글로벌한 비영리 활동은 상대적으로 너무 적어 국내 기업의 품질과 신뢰성 관련 기술 정보 수준은 사실 상당히 낮은 편에 속한다. 이와 같은 상황에서, 진정한 세계 일류를 꿈꾸는 것은 무리가 아닐까하는 생각을 지울 수가 없어 아쉬움이 크다.

2006년 필자는 SMT/PCB & NEPCON KOREA 전시회에 참가했고, 전시 기간 중 ESD 관련 글을 본 기억이 있다. 이 기간에 필자는 인근의 장소에서 ESD Workshop을 진행하고 있었다. 그 때의 기억을 아직도 잊을 수가 없다. 그 이유는 1989년에 이미 취소된 ESD 재료 측정 방법이 15년이 지난 서울에서 아직도 표준 방법으로 제시되고 있었기 때문이다.

필자는 한국의 전자 업계 기업의 새로운 변화와 전환을 희망하며 글을 마무리하고자 한다. 앞서가는 선진국, 그리고 우리를 바짝 뒤따라오는 중국과 동남아 기업들과의 경쟁에 앞서기 위해서는 한국기업과 한국 제품의 품질 경쟁력은 대단히 중요하다.

또한 앞서 설명한 바와 같이 반도체 소자의 기술 집적도가 높아짐에 따라 필연적인 ESD이슈는 다시 설명할 필요 없이 중요한 경영 요소이며, 제품의 품질과 신뢰성 관리에 있어 중요한 부분으로 떠오르고 있다.

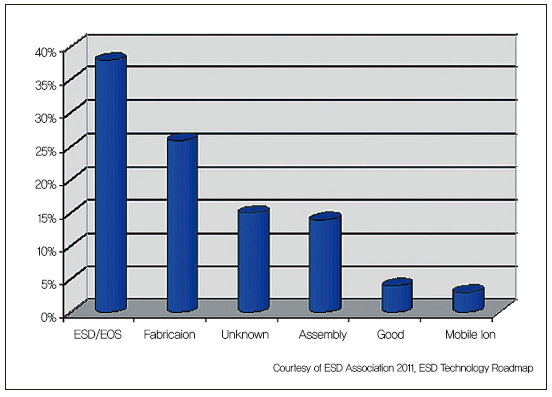

이는 필자 혼자만의 이야기가 아니다. ESD Association, 그리고 대부분의 반도체 제조업체에서 인정하고 있는 부분이다. 수백억 개의 소자 불량을 조사한 결과, No. 1 Root Cause는 EOS/ESD로 정리됐다(그림 4).

그림 4. 수백억 개의 소자 불량을 조사한 결과, No. 1 Root Cause는 EOS/ESD로 정리됐다.

이제 ESD 제어는 선택의 문제가 아닌 필수이다. 기업과 엔지니어들의 관심과 투자가 필요할 것으로 생각된다.

- 연재 순서 -

1. 표면실장 산업에서의 ESD 제어 현황과 국제표준과의 차이

2. ESD 관리 방법과 측정 기술

3. ESD 제어 재료와 Ionization 기술

4. ESD 불량 분석 기술

5. Device 테스트 방법과 System Level 테스트 방법

유용훈 대표 (코어인사이트)