[첨단 헬로티]

h파라미터와 등가 회로

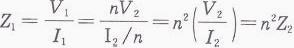

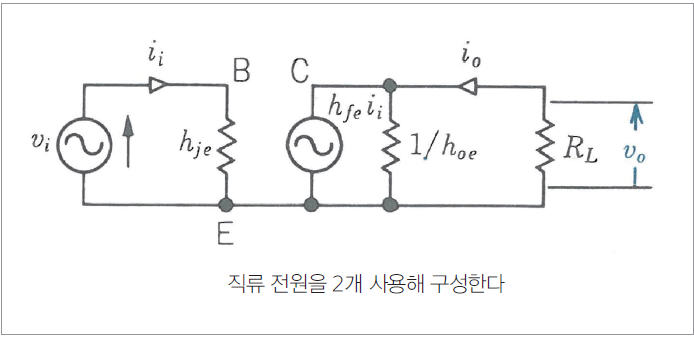

h파라미터란 트랜지스터가 할 수 있는 일을 이것과 똑같은 성질의 전기 회로로 고친 것을 트랜지스터의 등가 회로라고 한다. 만약 이미터 다자를 공통으로 해 트랜지스터를 4단자로 고쳐 놓은 회로를 생각할 때, 입력 전압 vi 입력 전류 ii, 출력 전압 vo, 출력 전류 io의 관계를 알 수 있다면 등가 회로를 사용해 이 회로의 성질을 알아낼 수 있게 된다[그림 1].

▲ 그림 1. 4단자로 취급한다

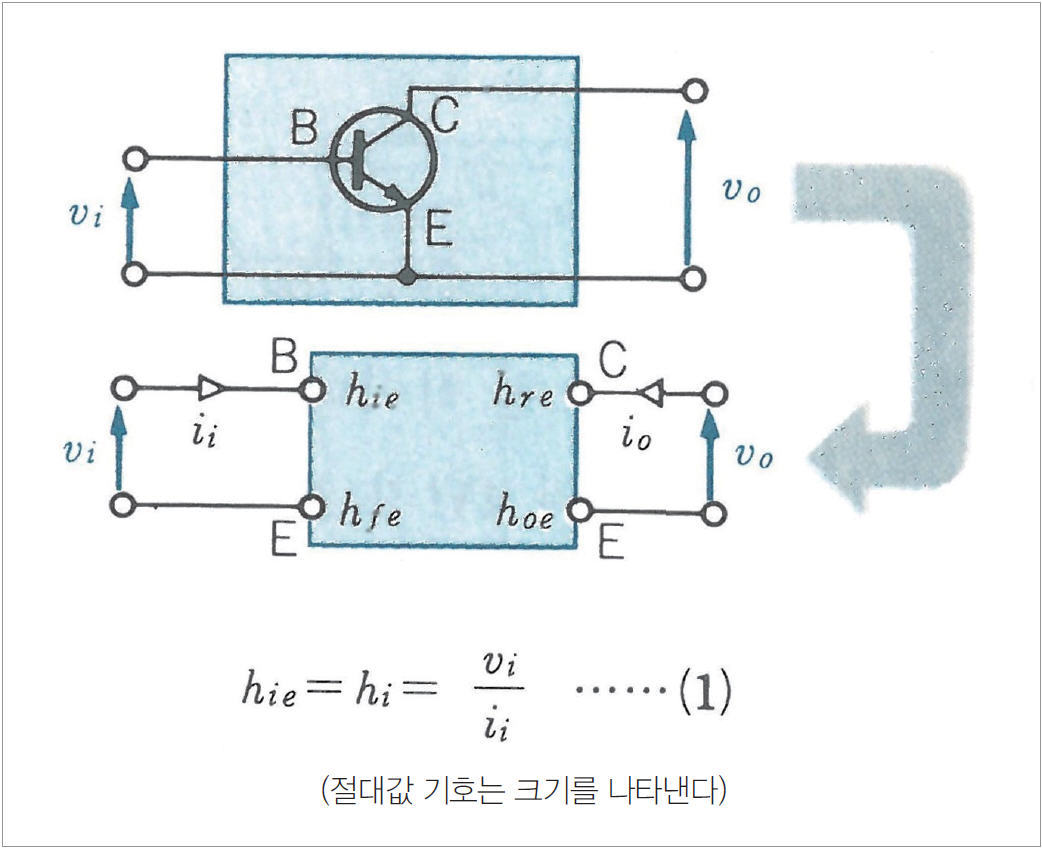

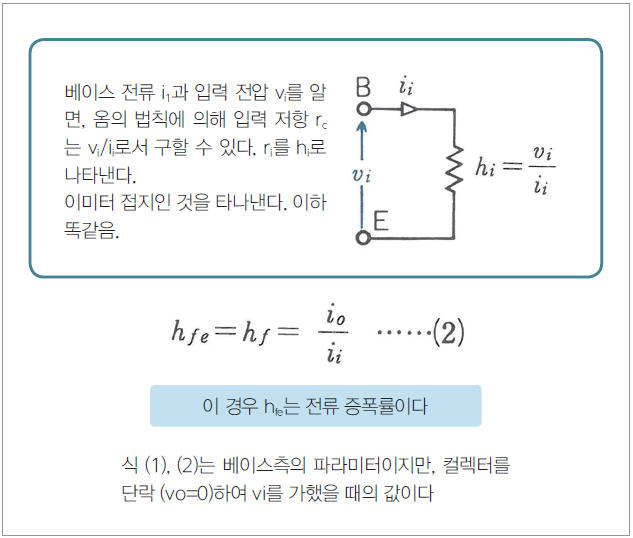

등가 회로를 사용하려면 위에서 나타낸 vi, ii, vo, io의 관계를 h파라미터라는 것이 필요하다. h파라미터는 [그림 1]과 [그림 2], [그림 3]의 설명에 의해 정의한 식 (1)~(4)와 같은 정수다. 이 값은 측정 조건에 따라서 변화하지만 대체로 다음과 같다.

▲ 그림 2. h파라미터의 의미

▲ 그림 3. h파라미터의 의미

hfe : 50~500 hie : 수 kΩ hre : 1 × 10-4

hoe : 10 × 10-6 ~ 30 × 10-5 [S](지멘스)

h파라미터를 사용해 [그림 1]의 기본적인 증폭 회로를 등가 회로로 고쳐 놓으면 [그림 4]와 같이 된다.

▲ 그림 4. 등가 회로

등가 회로를 h파라미터로 나타낸다

베이스측은 입력 전압 vi에 의해 베이스 전류 ii가 흐른다는 것은 이곳에 입력 저항 hie가 있기 때문인 것으로 생각한다. 또한 컬렉터측은 ii를 hfe배한 발전기(전류원으로 생각한다)에 의해 컬렉터 전류 io이 흐르며, 부하 저항 RL 양단에 출력 전압 vo가 생긴다고 생각한다. 전원에 포함되는 컬렉터 내부 저항은 1/hoe이므로 이것을 전원에 병렬로 붙여 놓는다. 이상으로 등가 회로가 완성된다. 이 등가 회로를 사용해 각 증폭도를 구할 수 있다(hoe는 생략).

이상의 식들은 근사식이지만 실용상 취급에는 별 문제가 되지 않는다. 그리고 트랜지스터의 h 정수는 접지 방식에 따라 그 값이 다르다.

바이어스 회로

바이어스(bias)란, 증폭하고 싶은 신호를 걸어줄 곳(이미터 접지에서의 베이스-이미터간)에, 미리 일정한 직류, 전류를 흘려주는 것이다. 또는 직류 전압을 걸어 놓는 것을 말한다.

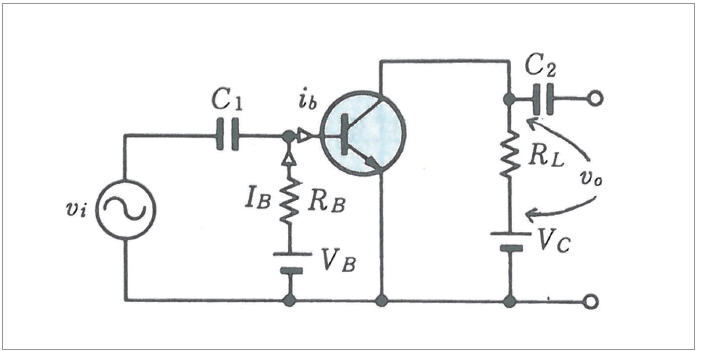

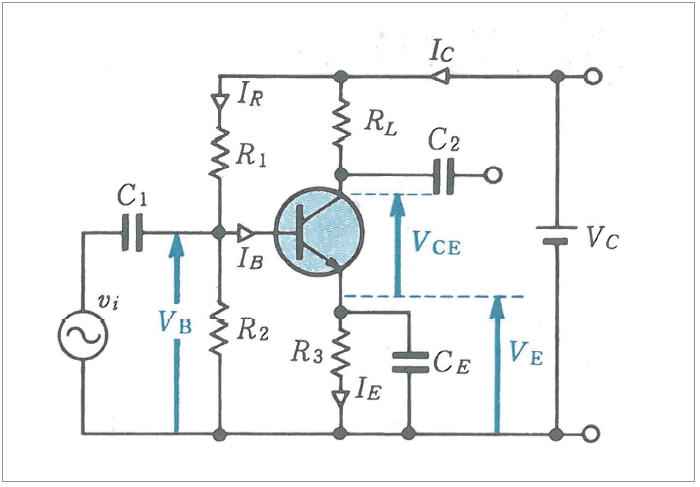

[그림 5]의 회로에서 입력 신호 vi에 의해 베이스 전류 ib가 흐르지만, 입력 신호의 진폭이 항상 양이 되도록 바이어스 전압 VB가 가해져 있다. 출력 전압 vo는 RL에 생기는 교루 신호분이므로 콘덴서 C2를 통해서 빼낼 수 있다.

▲ 그림 5. 바이어스 회로란

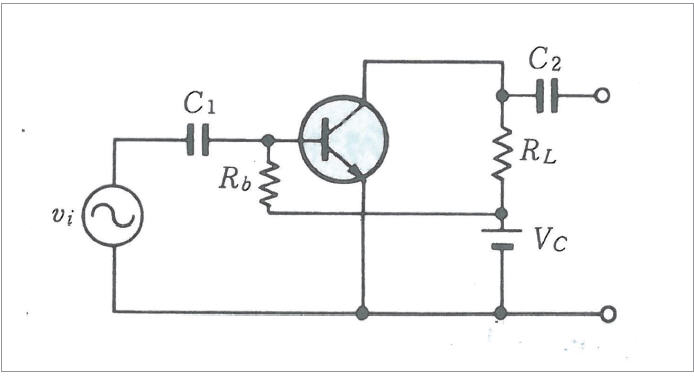

이 회로에서 직류 전원을 2곳에 사용하고 있으나 Vc만으로 컬렉터 전류 외에 베이스 전류 IB를 흘릴 수 있다. 고저항 Rb를 사용한 [그림 6]의 회로 방식을 고정 바이어스법이라 한다.

▲ 그림 6. 고정 바이어스

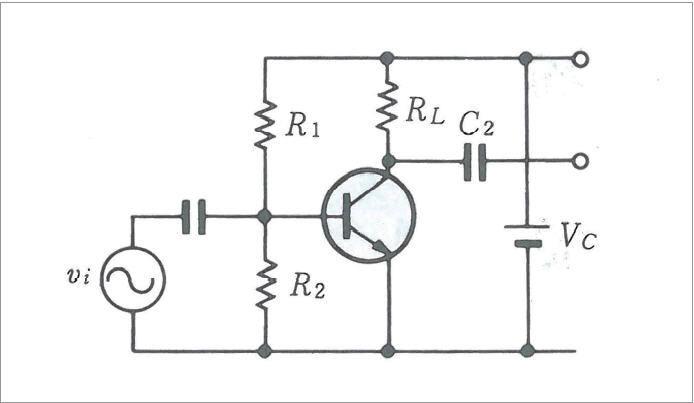

또한 [그림 7]처럼, R1과 R2의 두 저항을 사용해 VC를 분압하고, 이것을 B-E간에 약 0.6V가 되도록 하는 회로 방식을 분압 바이어스법이라 한다. 이와 같이 바이어스를 결정했다 하더라도 이것으로 안정한 증폭이 될 것이라고 간단히 말할 수 없다.

▲ 그림 7. 분압 바이어스

트랜지스터의 온도의 영향이나 전원 전압의 변동에 의해 그 동작점이 변동되기 쉽다. 그러므로 더욱 안정한 바이어스 회로가 필요하게 된다. 일반적인 회로의 예로서, [그림 8]과 같은 귀한(Feedback)에 의한 바이어스 회로의 동작을 알아보겠다.

▲ 그림 8. 직류 되먹임 바이어스 회로

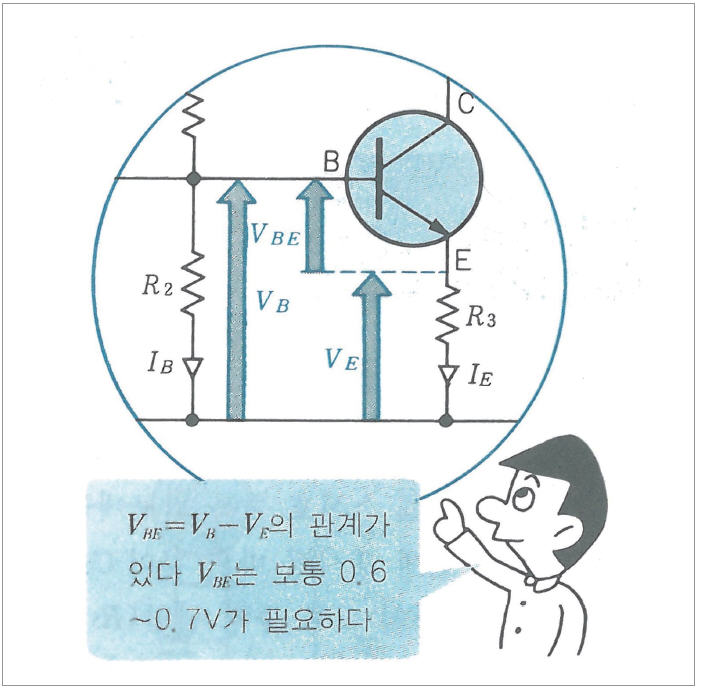

[그림 7]의 회로에 R3인 저항을 새로 이미터에 접속해 줌으로써 안정화시킬 수 있다. 즉 현재의 온도 상승에 의해 이미터 전류가 증가했다고 하면, 이미터 전압 VE가 커진다. 여기서 VB는 VC를 R1과 R2로 분압한 것이므로 일정하지만 트랜지스터 베이스-이미터간에 걸리는 바이어스 전압을 VB-VE가 되므로 감소하게 된다.

전류 귀환에 의한 바이어스의 안정화

[그림 9]처럼 베이스-이미터간에 실제로 가해지는 전압은 VB-VE인 것에 유의해야 한다. 따라서 베이스 전류는 감소하고, 온도 상승에 의한 컬렉터 전류의 필요 없는 증가를 막을 수 있게 된다. 그러나 R1, R2가 입력에 병렬로 들어가므로 입력 임피던스가 낮아지는 결점이 있다.

▲ 그림 9. VBE와 VB의 관계

이 경우 이미터 전류는 다음과 같다.

|

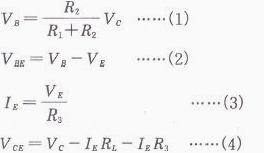

전류 귀환 바이어스의 간단한 계산법 바이어스 전륙와 전압의 간단한 계산법을 [그림 8], [그림 9]의 회로를 표본으로 익혀두자. 잊들은 보통 대략적인 값을 아는 것으로서 충분할 경우가 많다. 베이스 전류 IB는 IR, IE, IC에 비해 대단히 작으므로 이것을 무시하면 다음과 같은 식 (1)~(4)를 얻을 수 있다.

|

CR 결합 증폭 회로

트랜지스터의 동작을 이용한 것 중 증폭기로 대표적인 것은 저주파 증폭기다. 저주파라는 것은 고주파에 대한 상대적인 것으로서, 확실한 정의는 없지만 보통 수십 HZ부터 수십 kHz 정도의 음성 주파수를 말한다. 방송 전파 등의 음성 주파 출력은 대단히 미약하고 그 진폭이 작은 신호이므로 이들은 증폭하는 회로를 소신호 증폭 회로라고 부른다.

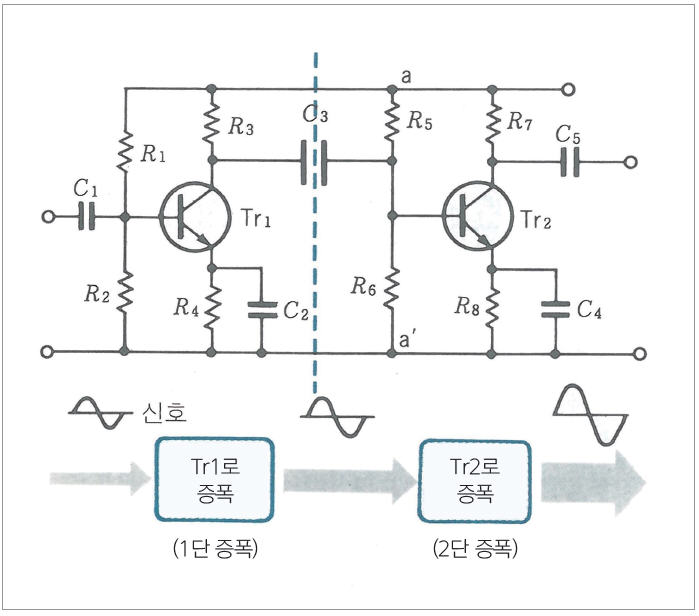

흔히 사용하는 소식호 증폭 회로에는 [그림 10]과 같은 CR 결합 증폭 회로가 있다. 이것은 회로에 표시된 바와 같이 C3(결합 콘덴서 또는 커플링(Coupling) 콘덴서라 부른다)로 앞단의 교류 출력 전압(R3 양단에 나타낸다)을 다음 단 베이스에 넘겨 보내는 일을 하는 것을 이용해 여러개의 트랜지스터를 종속 접속한 증폭기다.

[그림 10]은 CR 결합 2단 증폭기의 일반적인 회로이지만, 회로도 중의 점선 a-a’를 전후해 각각의 독립된 증폭단으로서의 분리해 비교해 보면 똑같이 구성된 회로가 종속으로 접속되어져 있는 것이다.

▲ 그림 10. CR 결합 2단 증폭 회로

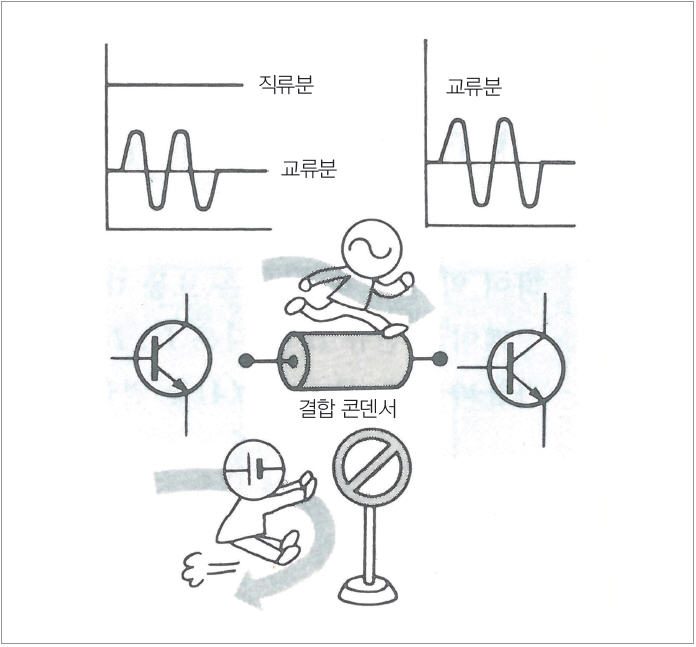

커플링 콘덴서 C3는 교류 출력 전압을 다음 단에 전하는 일 외에도 [그림 11]와 같이 직류분을 저지하는 일을 겸 한다.

▲ 그림 11. 직류분을 차단하는 콘덴서

그림에 대한 각 회로 소자의 역할을 나타내 보면 다음과 같다.

R1, R2, R5, R6……………Tr1, Tr2의 베이스 바이어스용 저항이다.

R3, R7………………………컬렉터 부항 저항으로 출력 전압을 발생시킨다.

R4, R8………………………트랜지스터의 바이어스를 안정시키는 이미터 저항이다.

C1, C3, C5…………………커플링 콘덴서로 직류를 저지하고 신호분만 통과시키다.

C2, C4………………………바이패스 콘덴서로 R4, R8 쪽에 교류분을 통하지 못하게 한다.

변성기 결합 증폭 회로

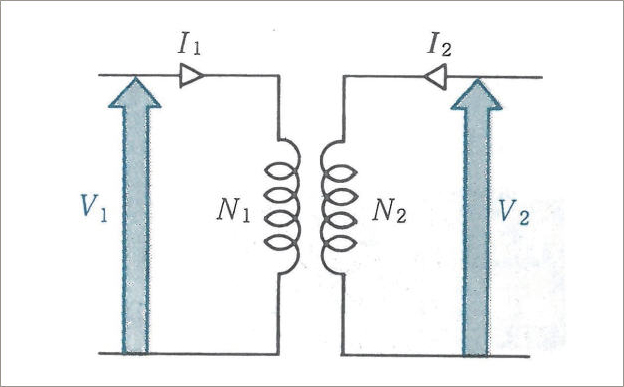

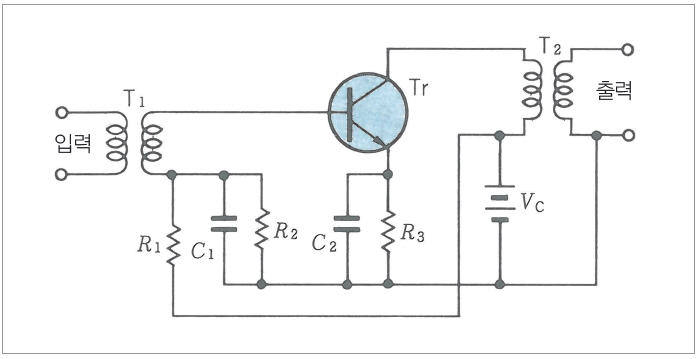

트랜지스터는 일반적으로 입력 임피던스가 낮고 출력 임피던스가 높기 때문에 그대로 다단 접속을 하여 증폭을 하면 1단당의 전력 이득이 낮아진다. 그런데 입출간을 [그림 12]와 같이 변성기를 사용해 임피던스 정합이 취해지게 한 회로를 변성기 결합 증폭 회로라고 한다. 부하에 직류가 통하지 못하고, 전원 전압을 유호하게 이용할 수 있기 때문에 낮은 전압으로 큰 전력 이득이나 출력 전력을 얻을 수 있다.

▲ 그림 12. 변성기(T1, T2) 결합 증폭기

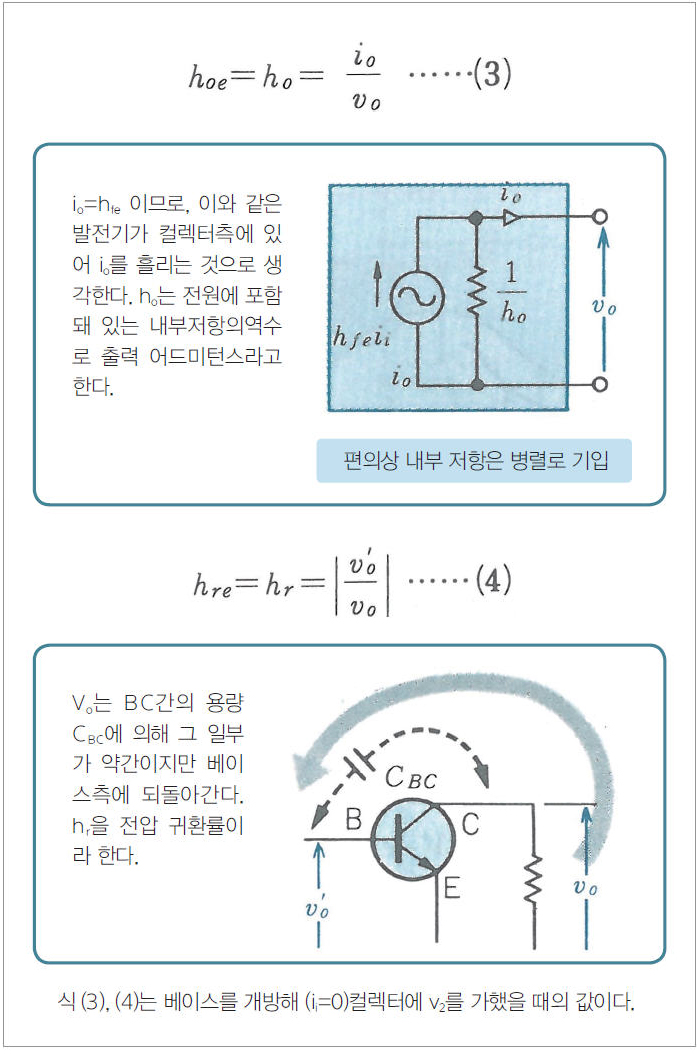

|

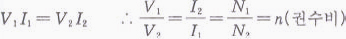

변성기 결합 회로는 권수비의 제곱에 비례하는 임피던스 변환이 되는 이유

▲ 그림 13. [그림 13]에 있어서 다음 관계가 성립된다.

2차측에서 본 임피던스 Z1은

|

* 전자기술이 반도체의 기초지식과 기술 이해를 돕기 위해 성안당의 <전자공학입문>을 연재합니다. <편집자 주>